Intel® 460GX Chipset Software Developer’s Manual 4-7

System Address Map

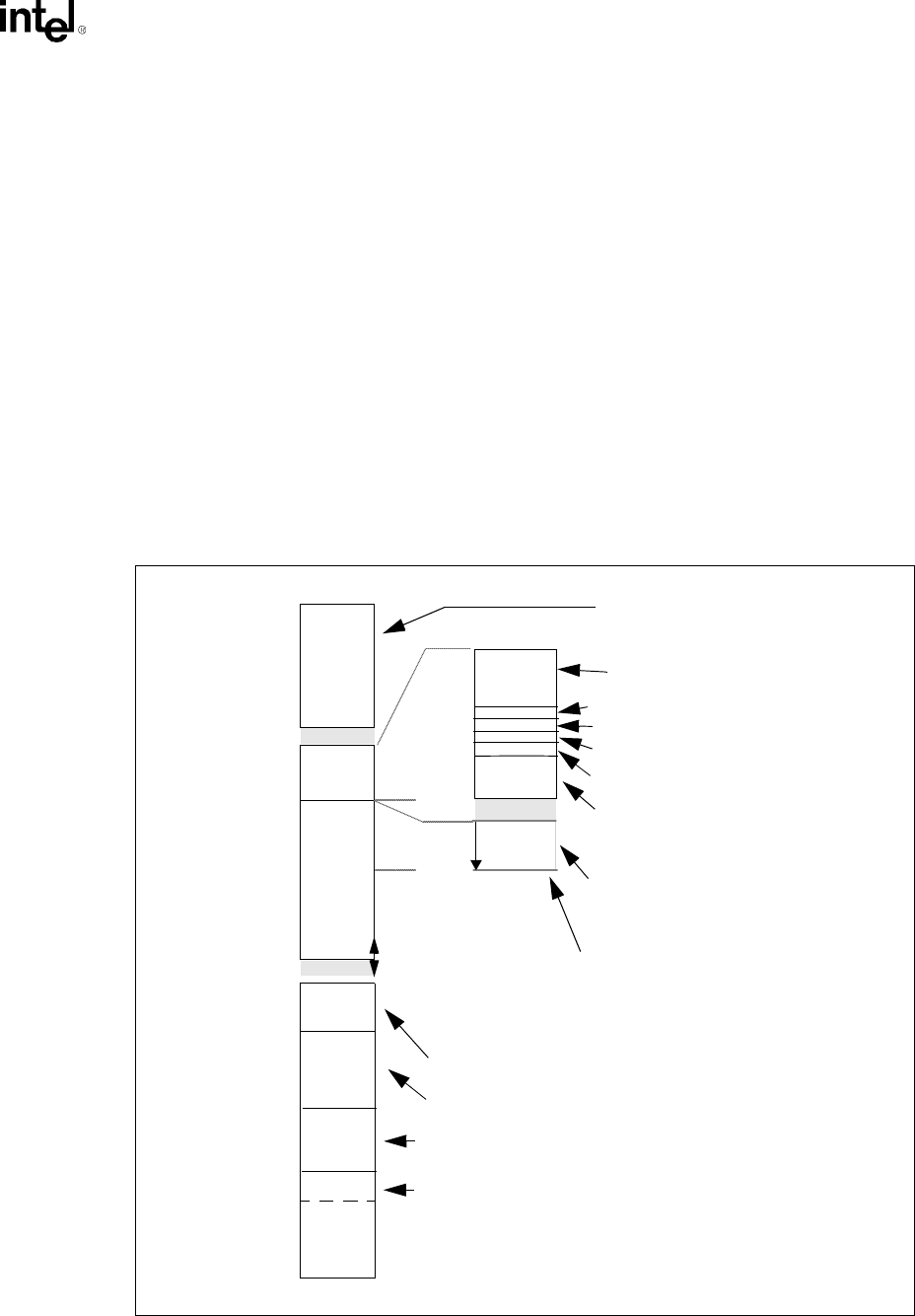

4.3 Devices View of the System Memory Map

Figure 4-1 shows an Expander Bridge device’s view of system memory. The goal is to prevent

invalid accesses at the expander bridge level, since different expander bridge devices are allowed

to access different regions. For example, PXBs are allowed to access other logical PCI segments

and GXBs are not. The SAC does not perform special checking to prevent this, and therefore the

expander bridges must be set up by firmware accordingly. An exception to this rule can be made if

the request is being routed to the system bus rather than directly to memory. For instance, accesses

above the Top of Memory are not blocked at the PXB level, but instead cause a BINIT# in the SAC

because they are guaranteed to go through the SAC’s decode logic since the PXB routes these

accesses to the system bus

Note: Figure 4-1 shows that parallel segment peer-to-peer accesses are only supported when initiated by

a PXB (GXBs are only allowed to initiate accesses directed to system memory) and directed to one

of the nx32M logical PCI segments (this segment can be anywhere except below the compatibility

PCI bus). Parallel segment peer accesses are not permitted anywhere below 1 MB, not even to the

VGA region. This means that if VGA is relocated below a GXB, a server management card on one

of the PCI buses in the system can no longer access the VGA range.

Figure 4-4. System Memory Address Space as Viewed from an Expander Bridge (PXB/GXB)

0

A_0000

C_0000

F_0000

10_0000

FEC0_0000

FF00_0000

FE00_0000

Chipset

System

32

Firmware,

Processor &

Chipset

Memory

Specific

System

1_0000_0000

Memory

FFF_FFFF_FFFF

MB

Specific

FFFF_FFFF

PCI Gaps

n x 32M

DOS

System

C, D, and E

Segments

VGA

Memory

Region

FE00_0000 -

(n x 32M)

High

System Firmware

PXB/GXB allow to interrupt delivery area

PXBs may support peer-to-peer; accesses

if enabled as memory GAP (directed to a logical PCI segment),

PXB must ignore

GXB must BINIT# after GART

PXB allows (only recommended to use

to the PXB’s own PCI bus must be ignored;

accesses to other PCI buses can be directed

to the system bus so the SAC forwards

them to the targeted peer bus

GXBs can not allow peer-to-peer; accesses

to the GXB’s own PCI bus must be ignored

(allows AGP card to “talk to itself” in that)

all PXB’s must ignore and all GXBs must BINIT# after GART

if enabled as memory GAP (directed to a logical PCI segment),

all PXB’s must ignore and all GXBs must ignore in the PCI stream

if enabled as memory GAP (directed to the compatibility PCI bus),

all PXB’s must ignore and all GXBs must BINIT# after GART

but BINIT# after GART (allows AGP card to “talk to itself” in that region)

after the GART must cause a BINIT#

region); accesses to any PCI bus that are found

PXB accesses above the Top of Memory

are routed as if to peer and therefore

go through the SAC decode and cause

Top of Memory

after the GART

a BINIT#; GXB must cause a BINIT#

All remaining regions are mapped to main memory and are always forwarded inbound

The term “ignore” from a PCI perspective means do not assert DEVSEL#;

Notes:

GXB must BINIT# after GART

PXB must ignore; GXB must BINIT# after GART

PXB defaults to memory so SAC must trap;

GXB must BINIT# after GART

4G-16M to 4G-17M

4G-17M to 4G-18M

4G-18M to 4G-19M

4G-19M to 4G-20M

instead allow request to master abort

using the “memory” route encoding

PXB must ignore; GXB must BINIT# after GART

from compatibility bus for server management)

if enabled as a memory GAP (directed to the compatibility PCI bus),

all PXB’s must ignore and all GXB’s must BINIT# after GART

512K-640K

Firmware