LPC/FWH Interface Configuration

11-22 Intel® 460GX Chipset Software Developer’s Manual

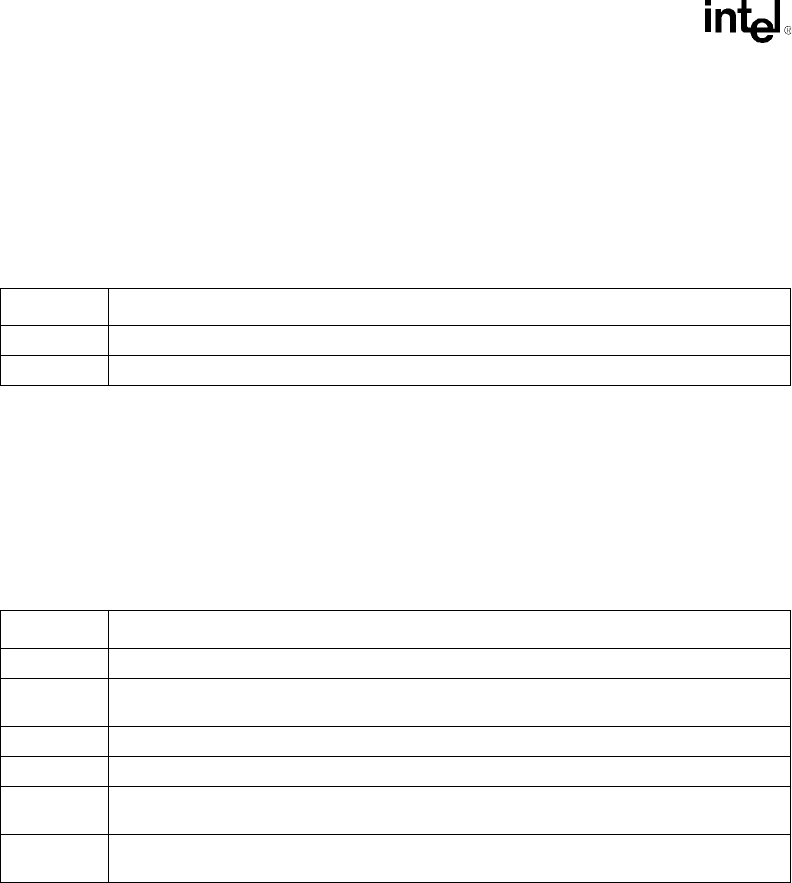

11.2.2.4 Icw3–Initialization Command Word 3 Register (I/O)

I/O Address: INT CNTRL-2–0A1h

Default Value: All bits undefined

Attribute: Write Only

On CNTRL-2 (the slave controller), ICW3 is the slave identification code broadcast by CNTRL-1.

11.2.2.5 Icw4–Initialization Command Word 4 Register (I/O)

I/O Address: INT CNTRL-1–021h; INT CNTRL-2–0A1h

Default Value: 01h

Attribute: Write Only

Both IFB interrupt controllers must have ICW4 programmed as part of their initialization

sequence.

11.2.2.6 Ocw1–Operational Control Word 1 Register (I/O)

I/O Address: INT CNTRL-1–021h; INT CNTRL-2–0A1h

Default Value: 00h

Attribute: Read/Write

OCW1 sets and clears the mask bits in the Interrupt Mask Register (IMR). Each interrupt request

line may be selectively masked or unmasked any time after initialization. The IMR stores the

interrupt line mask bits. The IMR operates on the IRR. Masking of a higher priority input does not

affect the interrupt request lines of lower priority. Unlike status reads of the ISR and IRR, for

reading the IMR, no OCW3 is needed. The output data bus contains the IMR when an I/O read is

active and the I/O address is 021h or 0A1h (OCW1). All writes to OCW1 must occur following the

ICW1-ICW4 initialization sequence, since the same I/O ports are used for OCW1, ICW2, ICW3

and ICW4.

Bit Description

7:3 Reserved. Must be programmed to all 0s.

2:0 Slave Identification Code. Must be programmed to 02h.

Bit Description

7:5 Reserved. Must be programmed to all 0s.

4 Special Fully Nested Mode (SFNM). Bit 4, SFNM, should normally be disabled by writing a 0

to this bit. If SFNM=1, the special fully nested mode is programmed.

3 Buffered mode (BUF). Must be programmed to 0 selecting non-buffered mode.

2 Master/Slave in Buffered Mode. Should always be programmed to 0. Bit not used.

1 AEOI (Automatic End of Interrupt). This bit should normally be programmed to 0. This is the

normal end of interrupt. If this bit is 1, the automatic end of interrupt mode is programmed.

0 Microprocessor Mode. Must be programmed to 1 indicating an Intel Architecture-based

system.