Intel® 460GX Chipset Software Developer’s Manual 13-9

Universal Serial Bus (USB) Configuration

3 Enter Global Suspend Mode (EGSM). 1=Host Controller enters the Global Suspend mode. No USB

transactions occur during this time. The Host Controller is able to receive resume signals from USB

and interrupt the system. Software resets this bit to 0 to come out of Global Suspend mode. Software

writes this bit to 0 at the same time that Force Global Resume (bit 4) is written to 0 or after writing bit

4 to 0. Software must also ensure that the Run/Stop bit (bit 0) is cleared prior to setting this bit.

2 Global Reset (GRESET). When this bit is set, the Host Controller sends the global reset signal on

the USB and then resets all its logic, including the internal hub registers. The hub registers are reset

to their power on state. This bit is reset by the software after a minimum of 10 ms has elapsed as

specified in Chapter 7 of the USB Specification.

Note: Chip Hardware Reset has the same effect as Global Reset (bit 2), except that the Host

Controller does not send the Global Reset on USB.

1 Host Controller Reset (HCRESET). When this bit is set, the Host Controller module resets its

internal timers, counters, state machines, etc. to their initial value. Any transaction currently in

progress on USB is immediately terminated. This bit is reset by the Host Controller when the reset

process is complete.

The HCReset effects on Hub registers are slightly different from Chip Hardware Reset and Global

USB Reset. The HCReset affects bits [8,3:0] of the Port Status and Control Register (PORTSC) of

each port. HCReset resets the state machines of the Host Controller including the Connect/

Disconnect state machine (one for each port). When the Connect/Disconnect state machine is reset,

the output that signals connect/disconnect are negated to 0, effectively signaling a disconnect, even

if a device is attached to the port. This virtual disconnect causes the port to be disabled. This

disconnect and disabling of the port causes bit 1 (connect status change) and bit 3 (port enable/

disable change) of the PORTSC to get set. The disconnect also causes bit 8 of PORTSC to reset.

About 64 bit times after HCReset goes to 0, the connect and low-speed detect will take place and bits

0 and 8 of the PORTSC will change accordingly.

0 Run/Stop (RS). 1=Run. 0=Stop. When set to a 1, the Host Controller proceeds with execution of the

schedule. The Host Controller continues execution as long as this bit is set. When this bit is set to 0,

the Host Controller completes the current transaction on the USB and then halts. The HC Halted bit

in the status register indicates when the Host Controller has finished the transaction and has entered

the stopped state. The Host Controller clears this bit when the following fatal errors occur:

consistency check failure, PCI Bus errors.

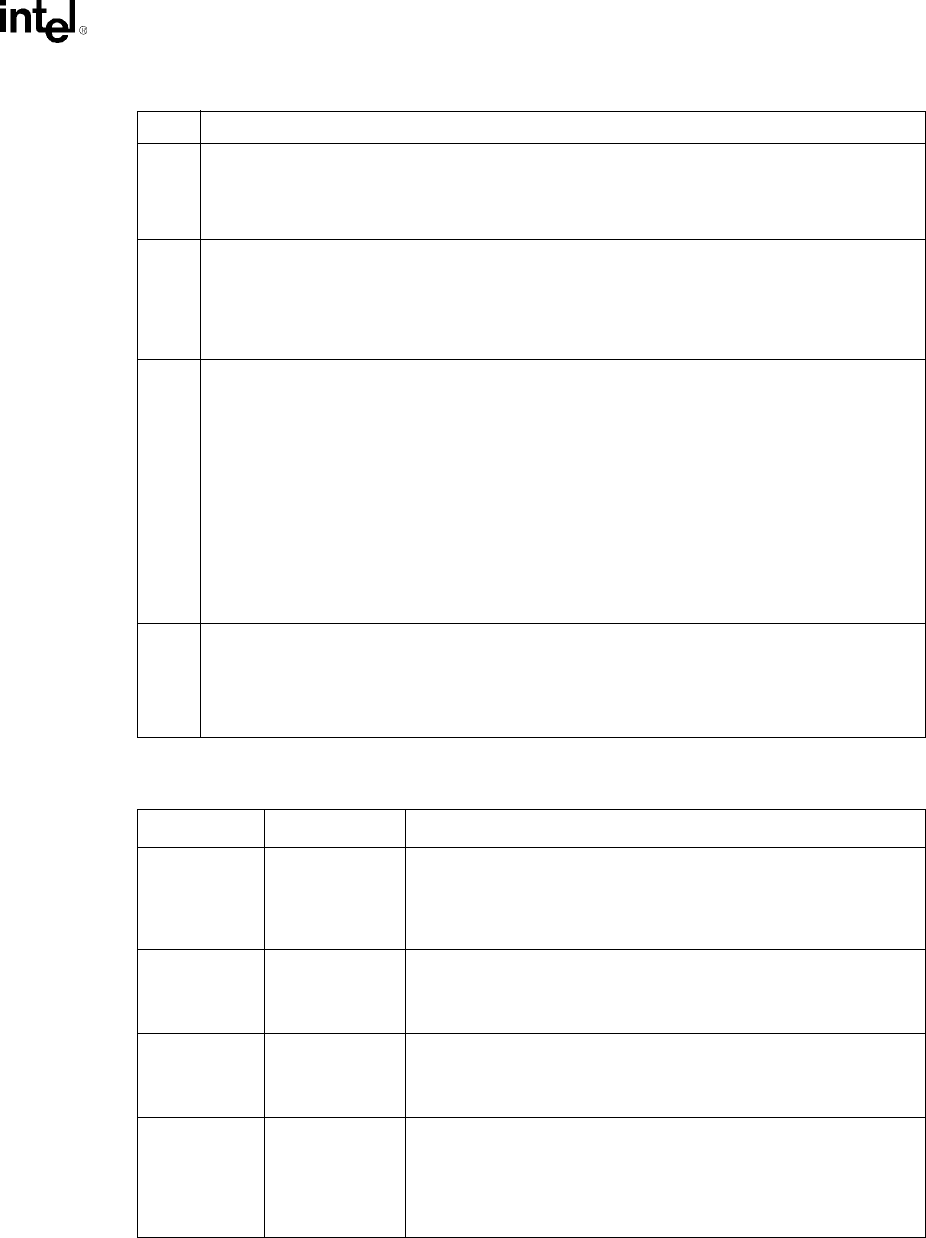

Table 13-2. Run/Stop, Debug Bit Interaction

SWDBG (Bit 5) Run/Stop (Bit 0) Operation

0 0 If executing a command, the Host Controller completes the command

and then stops. The 1.0 ms frame counter is reset and command list

execution resumes from start of frame using the frame list pointer

selected by the current value in the FRNUM register. (While Run/

Stop=0, the FRNUM register can be reprogrammed).

0 1 Execution of the command list resumes from Start Of Frame using the

frame list pointer selected by the current value in the FRNUM register.

The Host Controller remains running until the Run/Stop bit is cleared

(by Software or Hardware).

1 0 If executing a command, the Host Controller completes the command

and then stops and the 1.0 ms frame counter is frozen at its current

value. All status is preserved. The Host Controller begins execution of

the command list from where it left off when the Run/Stop bit is set.

1 1 Execution of the command list resumes from where the previous

execution stopped. The Run/Stop bit is set to 0 by the Host Controller

when a TD is being fetched. This causes the Host Controller to stop

again after the execution of the TD (single step). When the Host

Controller has completed execution, the HC Halted bit in the Status

Register is set.

Bit Description