Intel® 460GX Chipset Software Developer’s Manual 6-27

Data Integrity and Error Handling

Note: Additionally, error responses such as SERR#, XBINIT# and INTRQ# are predicated on both First

Error and Next Error contents since a second error may occur while the first error is in the process

of being serviced by the WXB hardware. Thus, for example, the system may observe an interrupt

associated with an error at almost the same instant XBINIT# is asserted for another.

For ease of isolation, the ERRSTS register records which of these registers have recorded an error.

6.12.4 Error Mask Bits

Many of the errors that the WXB handles have conditional reporting behavior. The error always

sets the appropriate bit(s) within the First Error or Next Error registers. For a subset of errors

additional information is also recorded in the PCI required PCISTS register. If the error is masked,

then an XBINIT# (or other specified action) will not occur, but the status bit indicating the

occurrence of the error is always set. This allows software to poll if it chooses, looking for errors

that are not considered as fatal to the system. The error logging information (associated only with

First Error) will always represent the first error identified since the register was last cleared

regardless of the masking of the particular error.

6.12.5 Error Steering/Signaling

All observed errors are recorded through status bits. In most cases these errors can be (optionally)

caused to signal the system that the error has occurred. Methods for signaling an error include

SERR#, XBINIT# and a P(A/B)INTRQ

1

interrupt. In the case of data parity errors, the minimal

response is to record the error and to simply forward the data on across the next interface with bad

parity. Table 6-2 lists the WXB error sources that are routable to one or more of the WXB error

signaling outputs. The error routing to SERR_OUT#, XBINIT#, and P(A/B)INTRQ as a function

of both ERRCMD and PCICMD register settings is presented in Table 6-3, Table 6-4, and

Table 6-5. Refer to the register definitions in Chapter 8 for more detail.

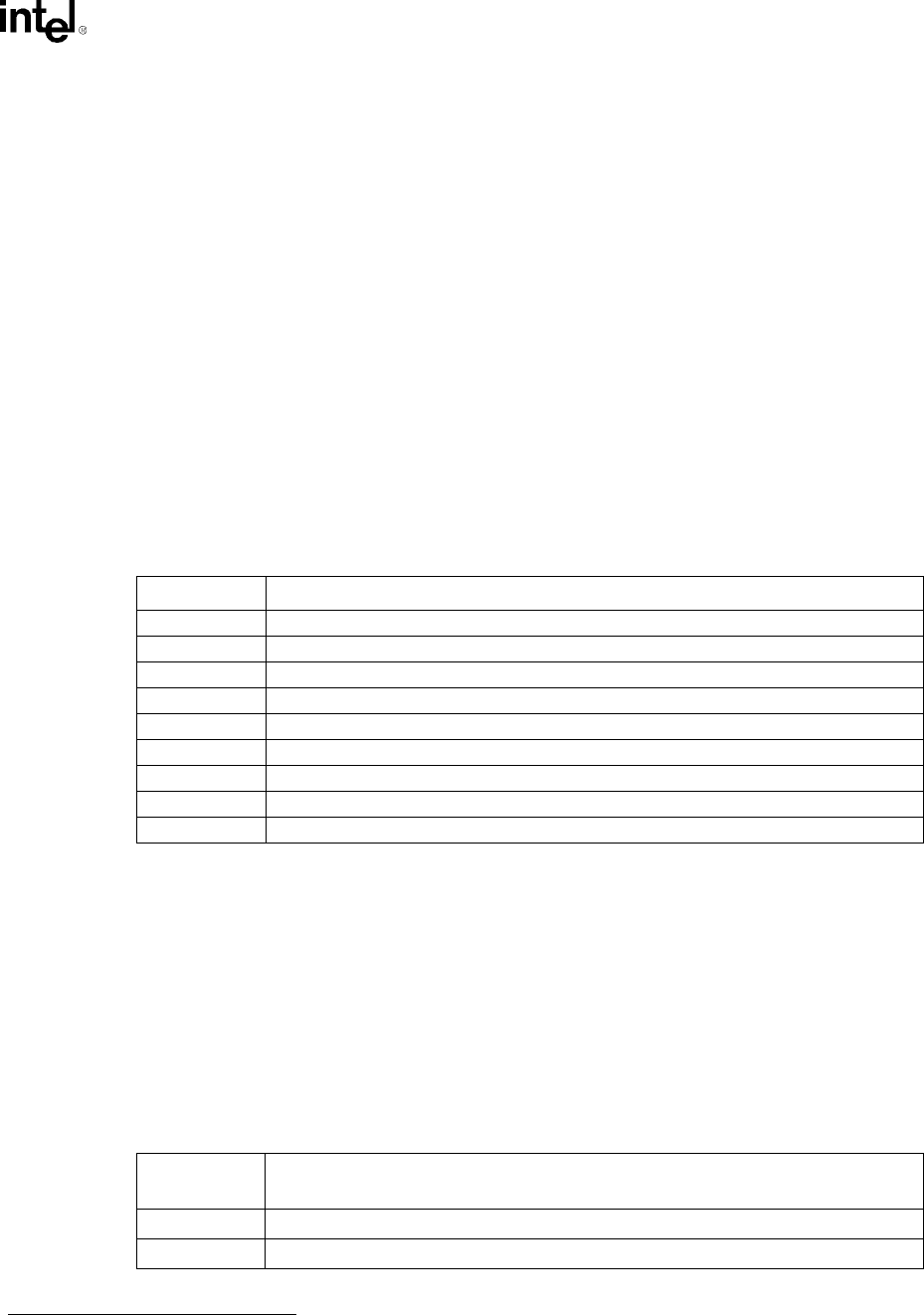

Table 6-2. List of WXB Error Sources Selectively Routable to XBINIT#, SERR_OUT#,

and P(A/B)INTRQ#

Abbreviation Error

APE PCI address parity error

CUIQ WXB RAM-generated data parity errors in transactions directed at WXB configuration space

DTE Inbound read discard timer expiration event

HPIQ WXB RAM-generated data parity errors in transactions destined to the IHPC

HPSERR IHPC-generated SERR

OPERR WXB-observed PERR# assertion

OSERR WXB-observed SERR# assertion

PCIDPE PCI bus data parity error

PUIQ WXB RAM-generated data parity errors in transactions destined to the PCI bus

1. See Section 6.12.6 for a description of the P(A/B)INTRQ interrupt.

Table 6-3. Supported Error Escalation to XBINIT#

a

a. To obtain the listed escalation, the following settings are required: XBINITE=’0’’.

XBINIT0

ERRCMD(15)

XBINIT#

Escalation

0 CUDPE, CUIQ, HPIQ, HP, IT, HLM, and MXBLK

1OFF