Intel® 460GX Chipset Software Developer’s Manual 11-17

LPC/FWH Interface Configuration

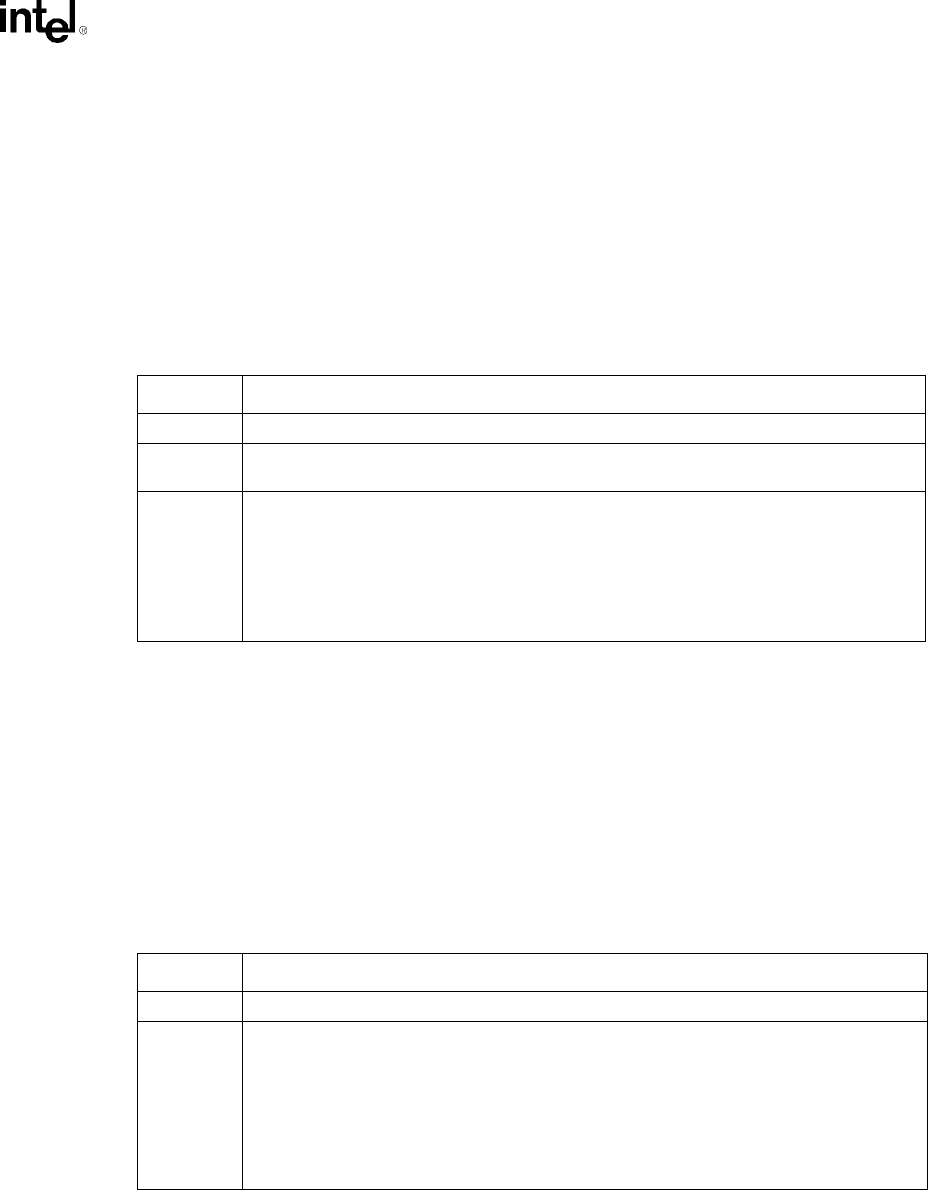

11.2.1.4 WSMB–Write Single Mask Bit (I/O)

I/O Address: Channels 0-3–0Ah; Channels 4-7–0D4h

Default Value: Bits[1:0]=undefined; Bit 2=1; Bits[7:3]=0 (CPURST or a Master Clear)

Attribute: Write Only

A channel's mask bit is automatically set when the Current Byte/Word Count Register reaches

terminal count (unless the channel is programmed for auto-initialization). Setting the entire register

disables all DMA requests until a clear mask register instruction allows them to occur. This

instruction format is similar to the format used with the DMA Request Register. Masking DMA

channel 4 (DMA controller 2, channel 0) also masks DMA channels [3:0].

11.2.1.5 RWAMB–Read / Write All Mask Bits (I/O)

I/O Address: Channels 0-3–0Fh; Channels 4-7–0DEh

Default Value: Bit[3:0]=1111; Bit[7:4]=0000 (CPURST or Master Clear)

Attribute: Read/Write

A channel's mask bit is automatically set to 1 when the Current Byte/Word Count Register reaches

terminal count (unless the channel is programmed for auto-initialization). Setting bits [3:0] to 1

disables all DMA requests until a clear mask register instruction enables the requests. Note that,

masking DMA channel 4 (DMA controller 2, channel 0), masks DMA channels [3:0]. Also note

that, Masking DMA controller 2 with a write to port 0DEh also masks DREQ assertions from

DMA controller 1.

Bit Description

7:3 Reserved. Must be 0.

2 Channel Mask Select. 1=Disable DREQ for the selected channel. 0=Enable DREQ for the

selected channel.

1:0 DMA Channel Select. Bits [1:0] select the DMA Channel Mode Register for bit 2.

Bits[1:0] Channel

00 Channel 0 (4)

01 Channel 1 (5)

10 Channel 2 (6)

11 Channel 3 (7)

Bit Description

7:4 Reserved. Must be 0.

3:0 Channel Mask Bits. 1=Disable the corresponding DREQ(s); 0=Enable the corresponding

DREQ(s).

Bit Channel

0 0 (4)

1 1 (5)

2 2 (6)

3 3 (7)