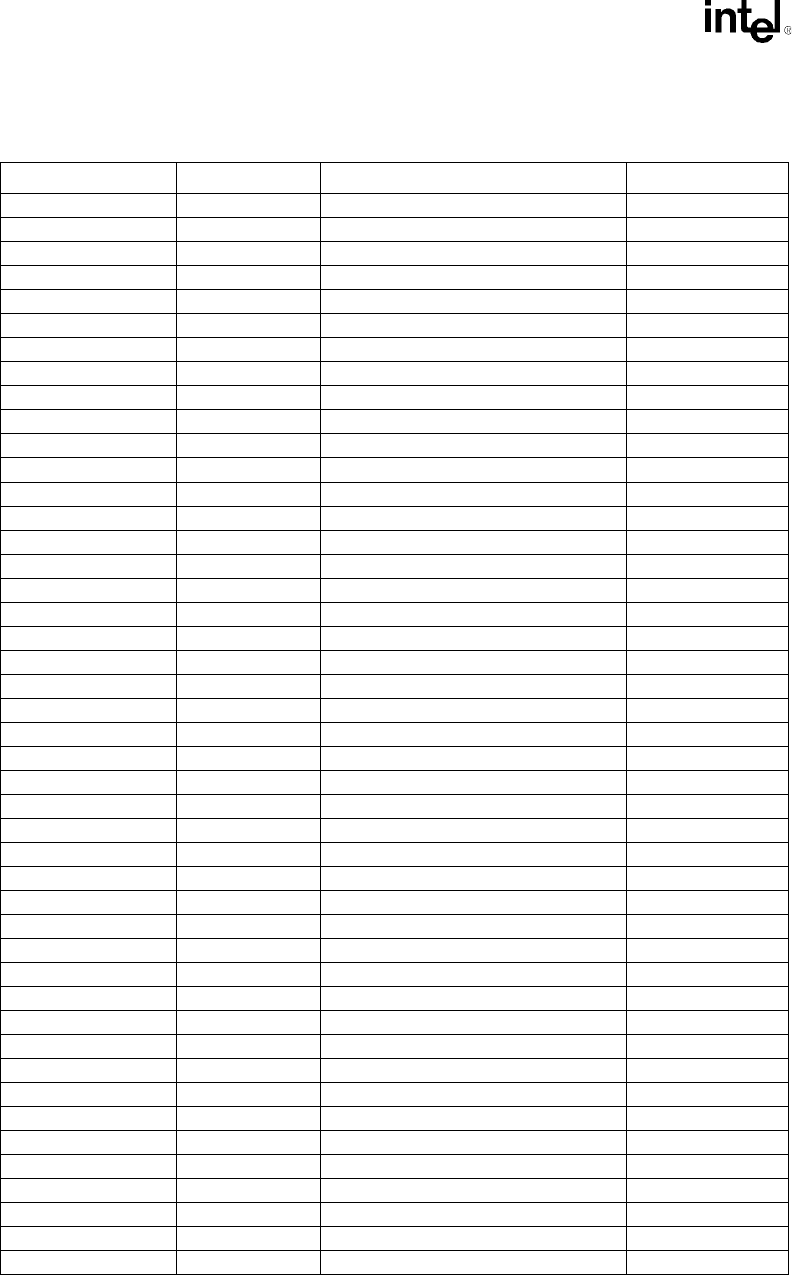

IFB Register Mapping

9-2 Intel® 460GX Chipset Software Developer’s Manual

06–07h PCISTS PCI Device Status R/W

08h RID Revision Identification RO

09-0Bh CLASSC Class Code RO

0C–0Dh – Reserved –

0Eh HEDT Header Type RO

0F–3Fh – Reserved –

40–43h ACPIBR ACPI Base Address Register R/W

44h ACPIEN ACPI Enable R/W

45h SCIRC Reserved R/W

46–4Bh – Reserved –

4Ch – Reserved R/W

4Dh – Reserved –

4E–4Fh BIOSEN Reserved R/W

50–5Fh – Reserved –

60–63h PIRQRC[A:D] Reserved R/W

64h SERIRQC Serial IRQ Control R/W

65–68h – Reserved –

69h TOM Top of Memory R/W

6A–6Bh MSTAT Miscellaneous Status R/W

6C–75h – Reserved –

76–77h – Reserved R/W

78–7Bh – Reserved R/W

7C–7Fh – Reserved –

80h – APIC Base Address Relocation R/W

81h – Reserved –

82h DLC Deterministic Latency Control R/W

83h – Reserved –

84–85h MGPIOC Muxed GPIO Control R/W

86–8Fh – Reserved –

90-91h PDMACFG PCI DMA Configuration R/W

92-95h DDMABASE Distributed DMA Slave Base Pointer R/W

96-C7h – Reserved –

C8h RTCCFG Real Time Clock Configuration R/W

C9–CFh – Reserved –

D0–D3h GPIOBA GPIO Base Address Register R/W

D4h GPIOE GPIO Enable R/W

D5–DFh – Reserved –

E0h LPCCD LPC COM Decode R/W

E1h LPCFD LPC FDD/LPT Decode R/W

E2h LPCSD LPC Sound Decode R/W

E3h FWHDE Firmware Hub Decode Enable –

E4–E5h LPCGD LPC Generic Decode Range R/W

E6–E7h LPCDE LPC Decode Enables R/W

E8h FWHS Firmware Hub Select –

E9–FFh – Reserved –

Table 9-1. PCI Configuration Registers–Function 0(PCI to LPC/FWH Interface Bridge)

(Cont’d)

Configuration Offset Mnemonic Register Register Access