AGP Subsystem

7-14 Intel® 460GX Chipset Software Developer’s Manual

7.3.1 Inbound Read Prefetching

The PCI protocol has no transfer size explicitly spelled out. Reads begin and continue until the

device has the data it needs. For performance, a PCI bridge could prefetch data ahead of when the

PCI device requests it. AGP, as opposed to PCI, has a length field in its protocol. Therefore the

graphics bridge does know how much data to fetch. Also the GXB has 1 GB/s peak into it, which is

the AGP peak, so there is no extra bandwidth in case the bridge prefetched the wrong data. For this

reason, the 460GX chipset will have no prefetching of graphics data. The graphics card should

have enough buffering and outstanding transactions to keep its pipes full. With pipelining, the card

can fetch the data it needs in advance of using it. Knowing what it wants to do, the graphics card

can prefetch only the data it expects to use. This allows the best utilization of the graphics port.

7.4 Latency

Latency of reads from the graphics card is an important parameter. Unfortunately it is difficult to

specify usefully. For an idle system, the latency of a graphics read will be 450-500 ns. For a

moderately loaded system, the latency of a read should be 600-900 ns. Defining ‘moderately

loaded’ is the difficult part. If the GXB queues are backed up servicing many small AGP requests,

then the latency may be much higher.

7.5 GXB Address Map

The ‘System Address Map’ chapter contains a section describing the what the system address map

looks like from the perspective of an expander bridge. This section is included to explicitly state

which address ranges must be checked at the AGP interface when using PCI protocol and which

ranges must be checked after GART translation.

There are two address regions which must be checked at the AGP bus interface when the card is

using PCI protocol: the GXB’s nx32M logical PCI space and the VGA space. This is required since

the AGP card may attempt to “talk to itself” using the PCI protocol in these regions, so the GXB

must not assert DEVSEL# to these accesses. The GXB’s nx32M region is specified using its

MMBASE and MMTOP registers. The VGA gap is enabled as a memory hole using the VGASE

register in the GXB. All other accesses using PCI protocol will receive DEVSEL#. This includes

accesses above TOM, in a MARG, etc. that may cause XBINIT# after the GART (see below).

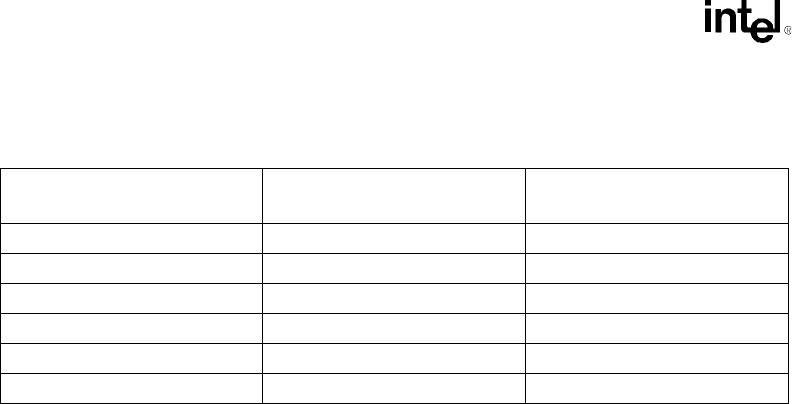

Table 7-5. Bandwidth Estimates for Various Request Sizes

Request Size

(in bytes)

Sustainable Bandwidth

(MB/s)

Latency (in ns.) for First Data

Returned on AGP Bus

8 100-300 500

16 250-500 500

32 450-700 530

64 750-850 600

128 850-925 750

256 800-850 1000