Intel® 460GX Chipset Software Developer’s Manual 13-11

Universal Serial Bus (USB) Configuration

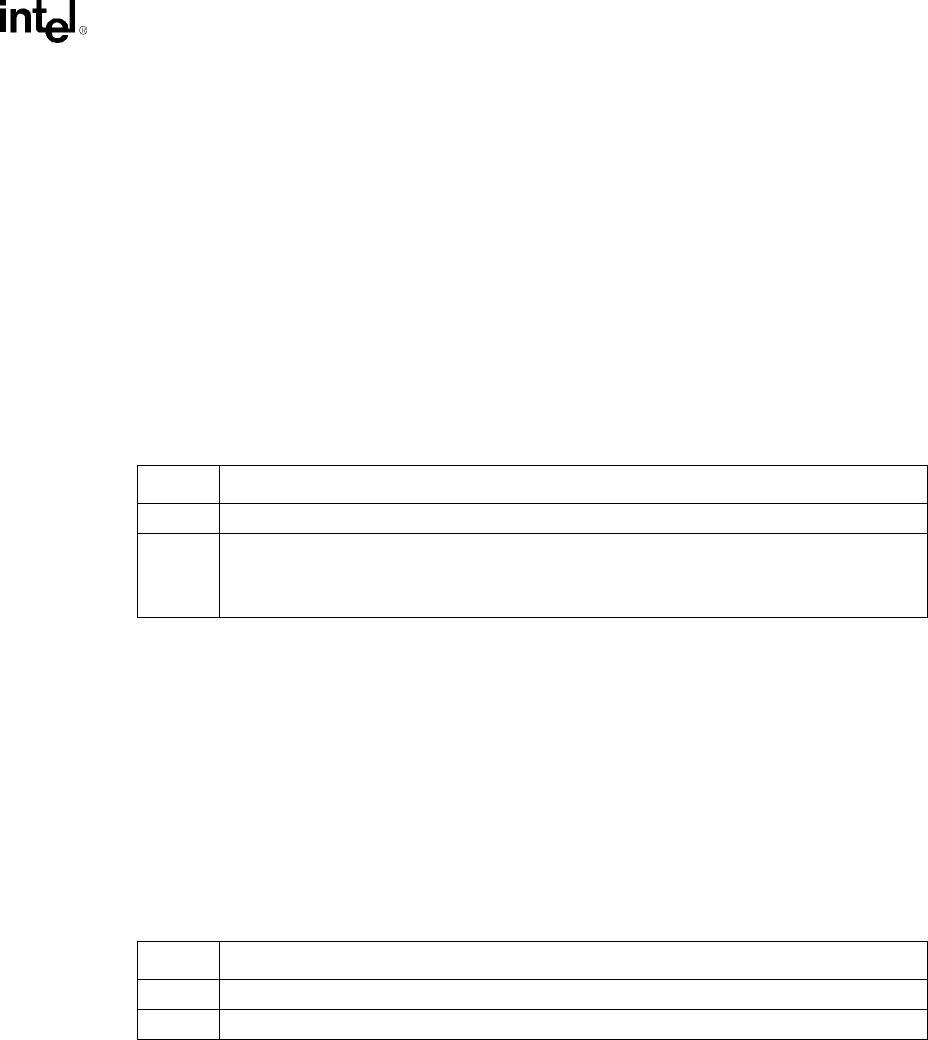

13.3.4 FRNUM–Frame Number Register (I/O)

I/O Address: Base + (06-07h)

Default Value: 0000h

Attribute: Read/Write (Writes must be Word Writes)

Bits [10:0] of this register contain the current frame number which is included in the frame SOF

packet. This register reflects the count value of the internal frame number counter. Bits [9:0] are

used to select a particular entry in the Frame List during schedule execution. This register is

updated at the end of each frame time.

This register must be written as a word. Byte writes are not supported. This register cannot be

written unless the Host Controller is in the STOPPED state as indicated by the HCHalted bit

(USBSTS register). A write to this register while the Run/Stop bit is set (USBCMD register) is

ignored.

13.3.5 FLBASEADD–Frame List Base Address Register (I/O)

I/O Address: Base + (08-0Bh)

Default Value: Undefined

Attribute: Read/Write

This 32-bit register contains the beginning address of the Frame List in the system memory. HCD

loads this register prior to starting the schedule execution by the Host Controller. When written,

only the upper 20 bits are used. The lower 12 bits are written as zero (4-Kbyte alignment). The

contents of this register are combined with the frame number counter to enable the Host Controller

to step through the Frame List in sequence. The two least significant bits are always 00. This

requires Dword alignment for all list entries. This configuration supports 1024 Frame List entries.

13.3.6 SOFMOD–Start of Frame (SOF) Modify Register (I/O)

I/O Address: Base + (0Ch)

Default Value: 40h

Attribute: Read/Write

This 1-byte register is used to modify the value used in the generation of SOF timing on the USB.

Only the 7 least significant bits are used. When a new value is written into the these 7 bits, the SOF

timing of the next frame will be adjusted. This feature can be used to adjust out any offset from the

clock source that generates the clock that drives the SOF counter. This register can also be used to

maintain real time synchronization with the rest of the system so that all devices have the same

sense of real time. Using this register, the frame length can be adjusted across the full range

Bit Description

15:11 Reserved.

10:0 Frame List Current Index/Frame Number. Bits [10:0] provide the frame number in the SOF

Frame. The value in this register increments at the end of each time frame (approximately every 1

ms). In addition, bits [9:0] are used for the Frame List current index and correspond to memory

address signals [11:2].

Bit Description

31:12 Base Address. These bits correspond to memory address signals [31:12], respectively.

11:0 Reserved. Must be written as 0s.