LPC/FWH Interface Configuration

11-26 Intel® 460GX Chipset Software Developer’s Manual

The Timer Control Word Register specifies the counter selection, the operating mode, the counter

byte programming order and size of the count value, and whether the counter counts down in a 16-

bit or binary-coded decimal (BCD) format. After writing the control word, a new count can be

written at any time. The new value takes effect according to the programmed mode.

Read Back Command

The Read Back Command is used to determine the count value, programmed mode, and current

states of the OUT pin and Null count flag of the selected counter or counters. The Read Back

Command is written to the Timer Control Word Register which latches the current states of the

above mentioned variables. The value of the counter and its status may then be read by I/O access

to the counter address. Note that The Timer Counter Register bit definitions are different during the

Read Back Command than for a normal Timer Counter Register write.

Counter Latch Command

The Counter Latch Command latches the current count value at the time the command is received.

If a Counter is latched once and then, some time later, latched again before the count is read, the

second Counter Latch Command is ignored. The count read will be the count at the time the first

Counter Latch Command was issued. If the counter is programmed for two byte counts, two bytes

must be read. The two bytes do not have to be read successively (read, write, or programming

operations for other counters may be inserted between the reads). Note that the Timer Counter

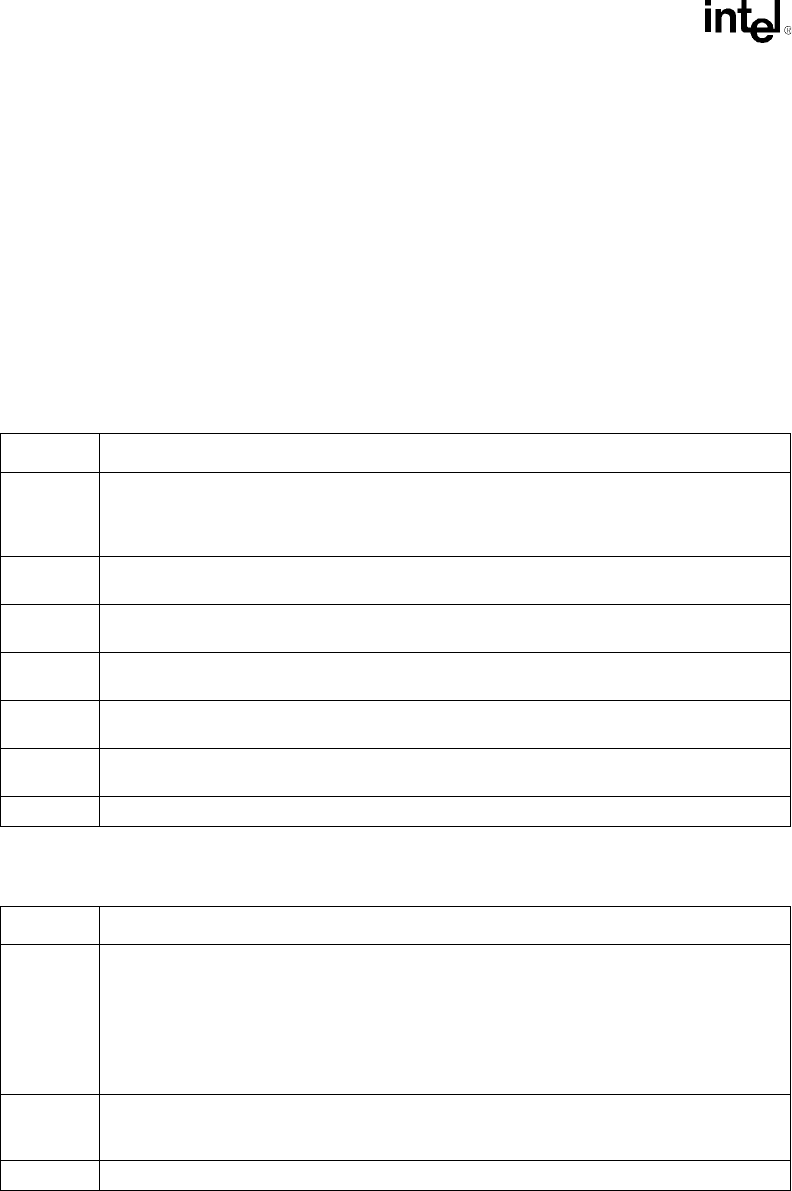

Bit Description

7:6 Read Back Command. When bits[7:6]=11, the Read Back Command is selected during a write

to the Timer Control Word Register. Following the Read Back Command, I/O reads from the

selected counter’s I/O addresses produce the current latch status, the current latched count, or

both if bits 4 and 5 are both 0.

5 Latch Count of Selected Counters. When bit 5=0, the current count value of the selected

counters will be latched. When bit 5=1, the count will not be latched.

4 Latch Status of Selected Counters. When bit 4=0, the status of the selected counters will be

latched. When bit 4=1, the status will not be latched.

3 Counter 2 Select. When bit 3=1, Counter 2 is selected for the latch command selected with bits

4 and 5. When bit 3=0, status and/or count will not be latched.

2 Counter 1 Select. When bit 2=1, Counter 1 is selected for the latch command selected with bits

4 and 5. When bit 2=0, status and/or count will not be latched.

1 Counter 0 Select. When bit 1=1, Counter 0 is selected for the latch command selected with bits

4 and 5. When bit 1=0, status and/or count will not be latched.

0 Reserved. Must be 0.

Bit Description

7:6 Counter Selection. Bits 6 and 7 are used to select the counter for latching.

Bit[7:6] Function

00 latch counter 0 select

01 latch counter 1 select

10 latch counter 2 select

11 Read Back Command select

5:4 Counter Latch Command. When bits[5:4]=00, the Counter Latch Command is selected during

a write to the Timer Control Word Register. Following the Counter Latch Command, I/O reads

from the selected counter’s I/O addresses produce the current latched count.

3:0 Reserved. Must be 0.