Universal Serial Bus (USB) Configuration

13-4 Intel® 460GX Chipset Software Developer’s Manual

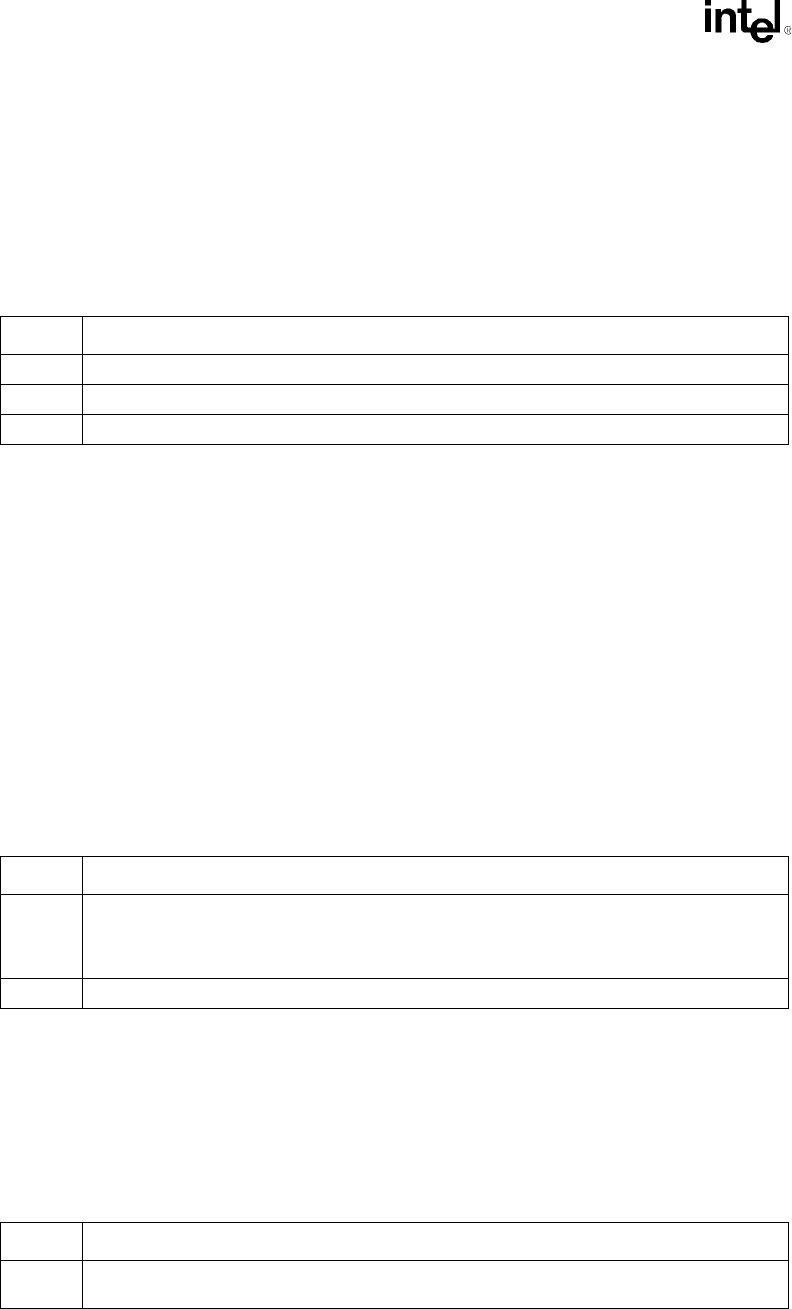

13.2.6 CLASSC–Class Code Register (Function 2)

Address Offset: 0A-0Bh

Default Value: 0C03h

Attribute: Read only

This register identifies the Base Class Code, Sub-Class Code, and Device Programming interface

for IFB PCI Function 2.

13.2.7 MLT–Master Latency Timer Register (Function 2)

Address Offset: 0Dh

Default Value: 00h

Attribute: Read/Write

MLT is an 8-bit register that controls the amount of time (in terms of PCI clocks) the USB module

can do transactions on the PCI bus. The count value is an 8 bit quantity, however MLT[3:0] are

reserved and assumed to be 0 when determining the count value. MLT is used when the USB

module becomes the PCI bus master and is cleared and suspended when IFB is not asserting

FRAME#. When IFB asserts FRAME#, the counter is enabled and begins counting. If the serial

bus module finishes its transaction before count is expired, the MLT value is ignored. If the count

expires before the transaction completes, IFB initiates a transaction termination as soon as the

current transaction is completed.. The number of clocks programmed in the MLT represents the

time slice (measured in PCI clocks) allotted to IFB, after which it must surrender the bus as soon as

the current transaction is completed.

13.2.8 HEDT–Header Type Register (Function 2)

Address Offset: 0Eh

Default Value: 00h

Attribute: Read only

This register identifies the Serial Bus module as a single Function device.

Bit Description

23:16 Base Class Code (BASEC). 0Ch=Serial Bus controller.

15:8 Sub-Class Code (SCC). 03h=USB Host Controller..

7:0 Programming Interface (PI). 00h=Universal Host Controller Interface.

Bit Description

7:4 Master Latency Counter Value. IFB initiated PCI cycles (including multiple transactions) can last

indefinitely as long as PHLDA# remains active. However, if PHLDA# is negated after a transaction

is initiated, IFB limits the duration of the transactions to the number of PCI bus clocks specified by

this field.

3:0 Reserved.

Bit Description

7:0 Device Type (DEVICET). 00. Multi-Function device capability for IFB is defined by the HEDT

register in Function 0.