SM Bus Controller Configuration

14-8 Intel® 460GX Chipset Software Developer’s Manual

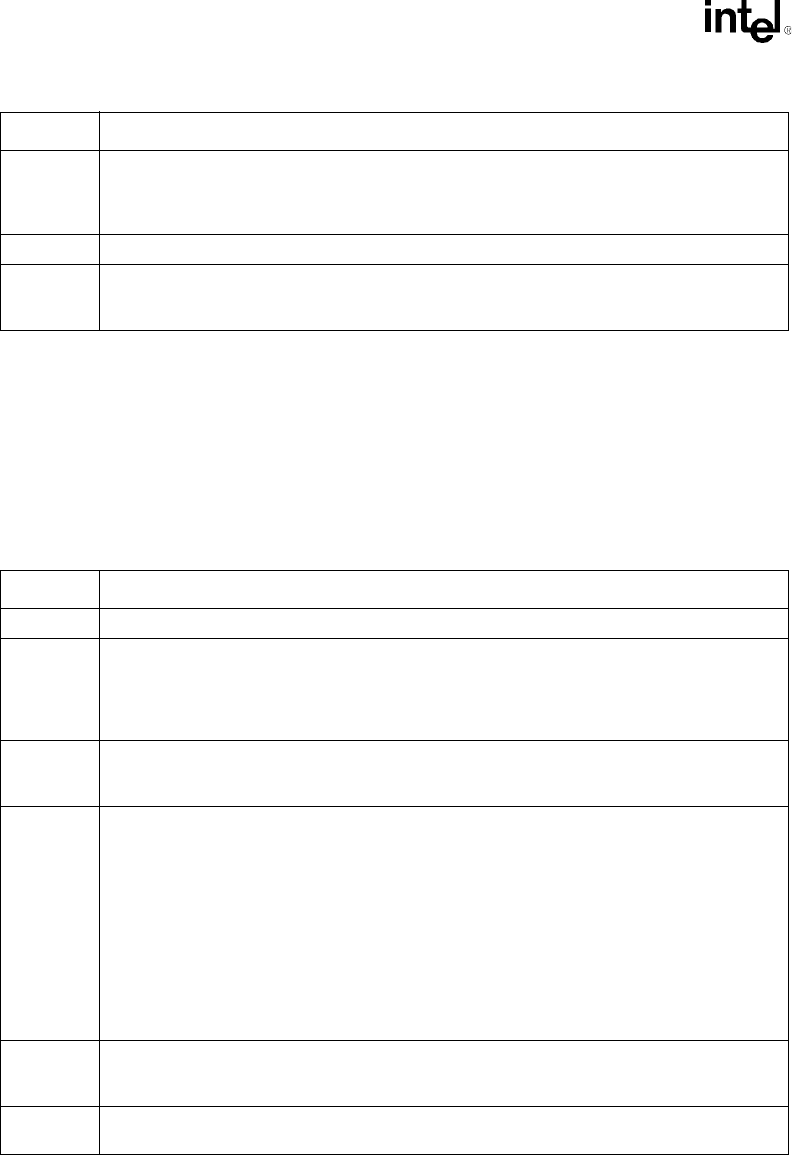

14.3.3 smbhstcnt–SMBus Host Control Register (I/O)

I/O Address: Base + (02h)

Default Value: 00h

Attribute: Read/Write

The control register is used to enable SMBus controller host interface Functions. Reads to this

register clears the host interface’s index pointer to the block data storage array.

2 Slave Status (SLV_STS)–R/WC. 1 = Indicates that the source of SMBus interrupt or resume

event was a slave cycle event match of the SMBSLVC (command match) and SMBSLVEVT

(data event match). 0 = SMBus interrupt not caused by slave event match. This bit is only set by

hardware and can only be reset by writing a 1 to this bit position.

1 Reserved.

0 Slave Busy (SLV_BSY)–RO. 1 = Indicates that the SMBus controller slave interface is in the

process of receiving data. 0 = SMBus controller slave interface is not processing data. None of

the other registers should be accessed if this bit is set.

Bit Description

Bit Description

7 Reserved.

6 Start (START)–R/W. 1 = Writing a 1 to this bit initiates the SMBus controller host interface to

execute the command programmed in the SMB_CMD_PROT field. All necessary registers

should be setup prior to writing a 1 to this bit position. 0 = Writing a zero has no effect. This bit

always reads zero. The HOST_BUSY bit can be used to identify when the SMBus host

controller has finished executing the command.

5 SMB_IDX_CLR: Any read to this register clears the slave interface’s internal index pointer to

the block SRAM array. This bit always reads zero, but exists as a reminder that reads to this

register clear the pointer index to the block SRAM array.

4:2 SMBus Command Protocol (SMB_CMD_PROT)–R/W. Selects the type of command the

SMBus controller host interface will execute. Reads or writes are determined by bit 0 of

SMBHSTADD register. This field is decoded as follows:

[4:2] Protocol

0,0,0 Quick Read or Write

0,0,1 Byte Read or Write

0,1,0 Byte Data Read or Write

0,1,1 Word Data Read or Write

1,0,0 Block Read or Write

1,0,1 Reserved

1,1,0 Reserved

1,1,1 Reserved

1 Kill (KILL)–R/W. 1 = Stop the current in process SMBus controller host transaction. This sets

the FAILED status bit and asserts the interrupt selected by the SMB_INTRSEL field. 0 = Allows

the SMBus controller host interface to Function normally.

0 Interrupt Enable (INTEREN)–R/W. 1 = Enable the generation of interrupts upon the completion

of the current host transaction. 0 = Disable.