System Address Map

4-8 Intel® 460GX Chipset Software Developer’s Manual

4.4 Legal and Illegal Address Disposition

Below is the disposition of addresses done by the Bus Interface Unit (BIU).

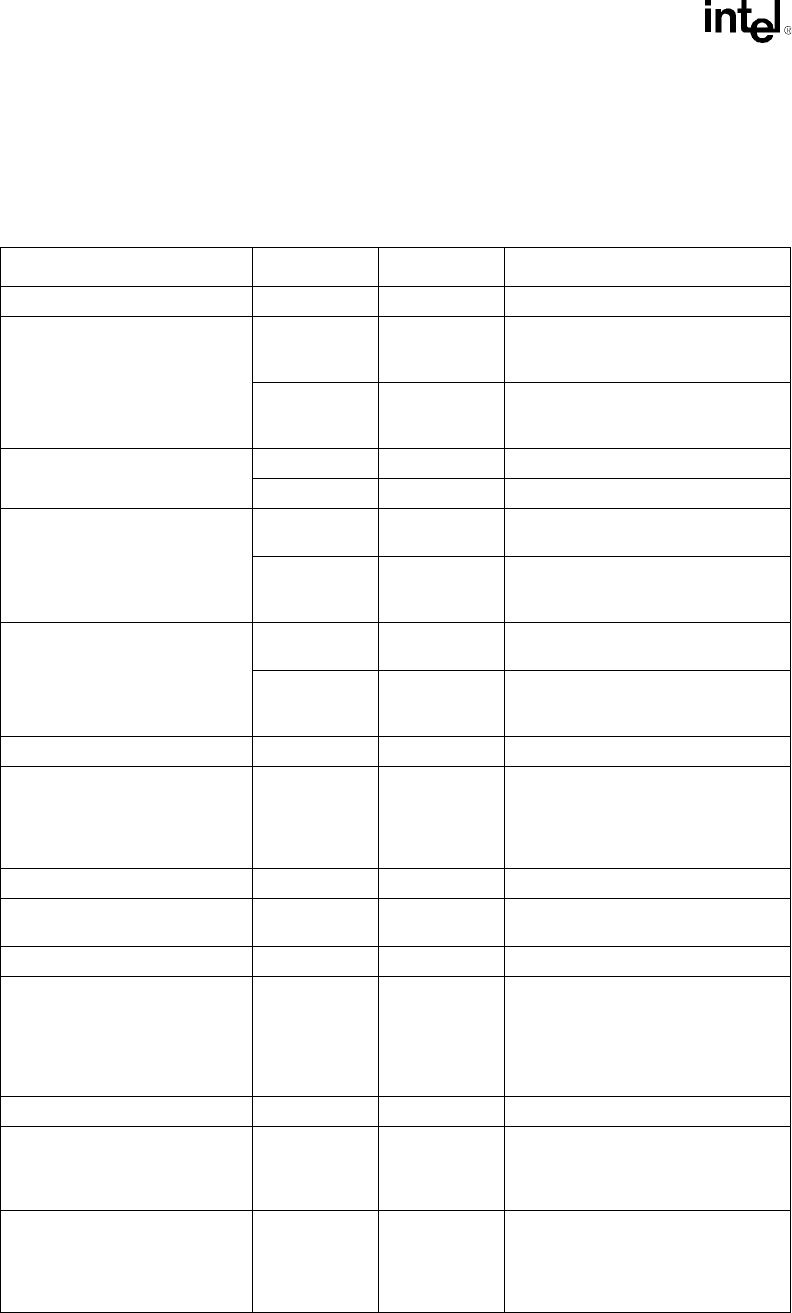

Table 4-1. Address Disposition

Address Range Outbound Inbound Dest. Decision

0-07FFFFh DRAM DRAM

080000h-09FFFFh DRAM DRAM MAR=11 or (Read and MAR= 01 and

no system bus LOCK#) or (Write and

MAR = 10)

PCI0a unclaimed MAR=00 or (Read and MAR=01 and

system bus LOCK#) or (Read and

MAR=10) or (Write and MAR=01)

0A0000h-0BFFFFh DRAM DRAM VGASE=0

PCIx unclaimed VGASE=1

0C0000h-0EFFFFh

(divided into 12 regions of 4k

bytes)

DRAM DRAM MAR=11 or (Read and MAR= 01 and

no LOCK#) or (Write and MAR = 10)

PCI0a unclaimed MAR=00 or (Read and MAR=01 and

LOCK#) or (Read and MAR=10) or

(Write and MAR=01)

0F_0000h-0F_FFFFh DRAM DRAM MAR=11 or (Read and MAR= 01 and

no LOCK#) or (Write and MAR = 10)

PCI0a unclaimed MAR=00 or (Read and MAR=01 and

LOCK#) or (Read and MAR=10) or

(Write and MAR=01)

10_0000h - PCIS[7] DRAM DRAM PXB uses LXGB instead of PCIS[7]

PCIS[7] - FDFF_FFFFh PCIx PCIx PCIS register determines target PCI

bus

On PCI if

MMBASE<=address<=MMT, then not

claimed. GXB: unclaimed

FE00_0000h-FE1F_FFFFh undefined undefined This region is reserved.

FE20_0000h-FE3F_FFFFh Expander port-

2 or PCI0A

Expander port

2 or PCI0A

If DEVNPRES[14]=0, send to

Expander port 2, else send to PCI-0a

FE40_0000h-FE5F_FFFFh undefined

undefined This region is reserved.

FE60_0000h to FEBF_FFFFh Config unit or

PCI-0a

Config unit or

PCI-0a

If <=8B then: if one of defined

registers read or write value, if not

then return all 1’s or terminate writes.

If >8B, then send to PCI-0a. NOTE:

Locks to this range are forbidden and

will hang the system

FEC0_0000 to FECF_FFFFh PCI x unclaimed SAR, IOABASE (PXB)

FED0_0000h to FEDF_FFFFh PCI 0a or

dropped

PXB will

forward IB and

mark it to

memory.

Reads are sent to PCI-0a for master

abort. Writes get No-Data response

and are dropped

FEE0_0000h to FEEF_FFFFh Interrupt

Transaction;

Reads sent to

PCI 0a, writes

dropped

interrupt for IB

write, PCI-0a

for read

Reads are sent to PCI-0a for master

abort. IB writes are turned to

interrupts. OB writes get No-Data

response and are dropped