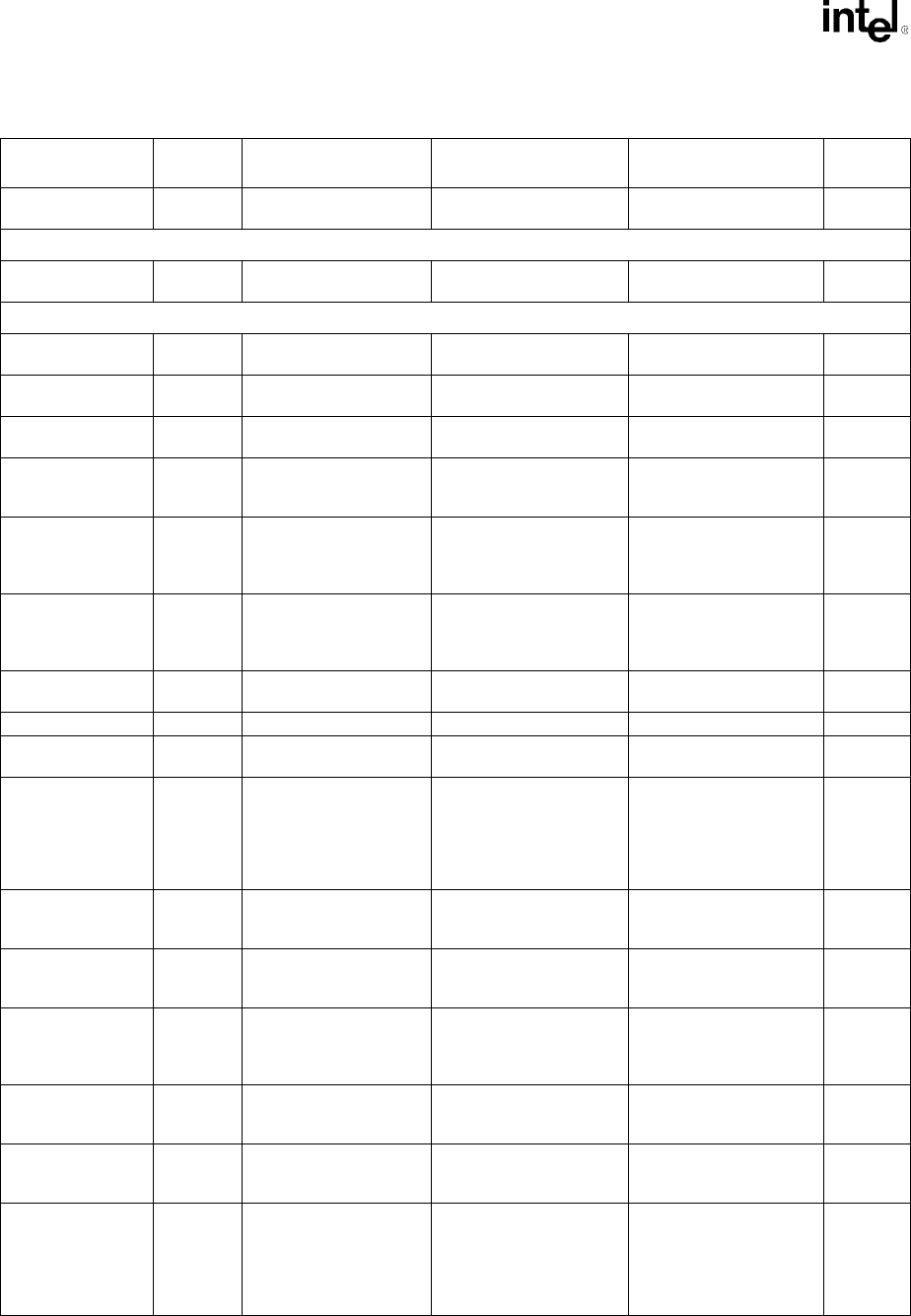

Data Integrity and Error Handling

6-18 Intel® 460GX Chipset Software Developer’s Manual

‘Accept’ Underflow SDC Unconditional BINIT# SDC_FERR[AEx],

FERR_SAC[SFE]

Nothing

Internal SDC Error

Data Buffer Ram

Parity Error

SDC Unconditional Interrupt SDC_FERR[RPE],

FERR_SAC[SNE]

Nothing

GXB ERRORS

AGP Request

Queue Overflow

GXB Unconditional XBINIT# FERR_AGP Nothing

Use of Pipe with

Sideband Enabled

GXB Unconditional XBINIT# FERR_AGP Nothing

AGP Address [

..36] not = 0

GXB Unconditional XBINIT# FERR_AGP Nothing

Unsupported

command using

AGP semantics

GXB Unconditional XBINIT# FERR_AGP Nothing

PCI IB Read Que

Data Parity Error

GXB Conditional XINTR#

Conditional XBINIT#

FERR_PCI Nothing TXDERR

_INTE,

TXDERR

_BINITE

PCI OB Write Que

Data Parity Error

GXB Conditional XINTR#

Conditional XBINIT#

FERR_PCI Nothing TXDERR

_INTE,

TXDERR

_BINITE

Discard timer

expiration

GXB Unconditional XINTR#

SERR# if SERRE set

FERR_PCI Nothing

SERRE

SERR# Observed GXB Unconditional XINTR# FERR_PCI Nothing

PERR# Observed GXB Unconditional XINTR# FERR_PCI,

possibly PCISTS[DPE]

Nothing

PCI Parity Error on

Address from Card

GXB Let card master abort;

SERR# and XINTR# if

SERRE set; if SERRE

not set then neither

SERR# nor XINTR#

driven.

PCISTS[PE],

FERR_PCI,

possibly PCISTS[SSE]

PAC_ERR

SERRE

PCI Parity Error on

Data from Card

GXB Data placed into queue

with bad parity.

Conditional PERR#

PCISTS[PE],

PCISTS[DPE] if PERRE

PD_ERR, PAC_ERR PCICM

[PERRE]

Master Abort on

Read by GXB

GXB 1DW: Return all 1’s

> 1DW: Hard Fail (HF)

completion.

PCISTS [RMA],

FERR_PCI

Nothing

Master Abort on

Write done by GXB

GXB 1 DW: normal

completion

>1 DW: Hard Fail (HF)

completion.

PCISTS [RMA],

FERR_PCI

Nothing

Master Abort on

Configuration

Cycle

GXB Normal completion PCISTS [RMA]

(FERR_PCI is not set)

Nothing

Target Abort on

Transaction

Mastered by GXB

GXB Return HF to either read

or write.

PCISTS [RTA],

FERR_PCI

Nothing

GART Entry Invalid GXB Unconditional XINTR#,

Conditional XBINIT#.

(NOTE: if XBINIT# is

driven, then it is not

required to drive

XINTR#)

FERR_GART Nothing GARTINV

_BINITE

Table 6-1. Error Cases (Cont’d)

Error

Chip

Detecting

System

Action

Status

Register

Log

Register

Qualifier