Intel® 460GX Chipset Software Developer’s Manual 12-11

IDE Configuration

12.3.3 BMIDTPx–Bus Master IDE Descriptor Table Pointer Register

(I/O)

Address Offset: Primary Channel–Base + 04h; Secondary Channel–Base + 0Ch

Default Value: 00000000h

Attribute: Read/Write

This register provides the base memory address of the Descriptor Table. The Descriptor Table must

be DWord aligned and not cross a 4 KByte boundary in memory.

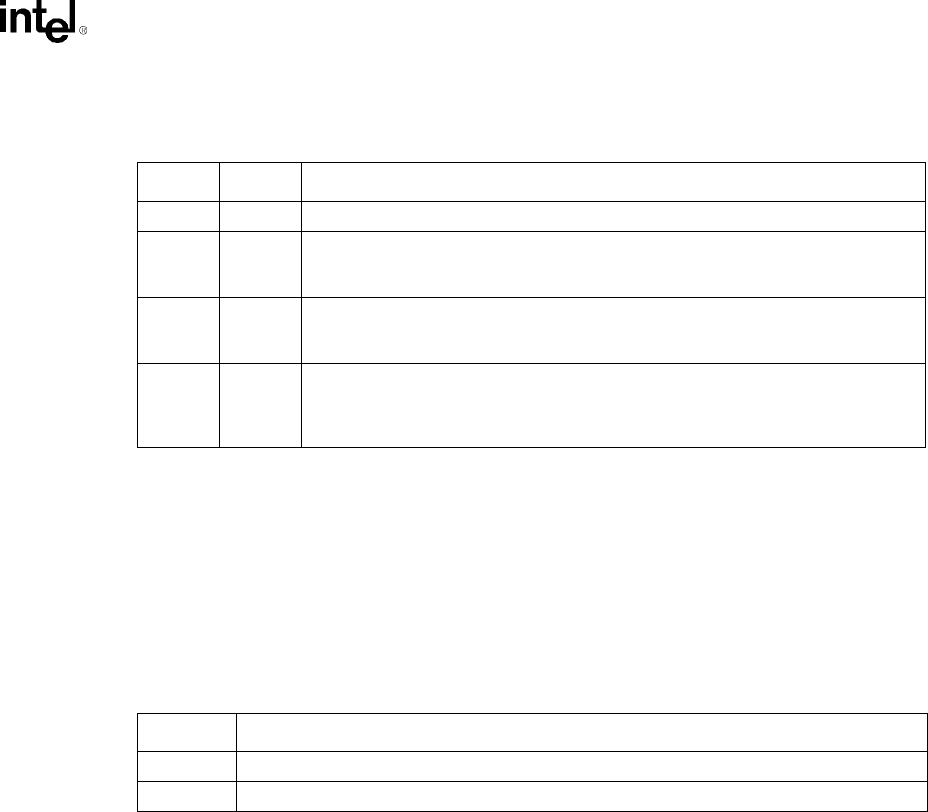

Table 12-4. Interrupt/Activity Status Combinations

Bit 2 Bit 0 Description

01DMA transfer is in progress. No interrupt has been generated by the IDE device.

10The IDE device generated an interrupt and the Physical Region Descriptors

exhausted. This is normal completion where the size of the physical memory regions

is equal to the IDE device transfer size.

11The IDE device generated an interrupt. The controller has not reached the end of

the physical memory regions. This is a valid completion case when the size of the

physical memory regions is larger than the IDE device transfer size.

00Error condition. If the IDE DMA Error bit is 1, there is a problem transferring data to/

from memory. Specifics of the error have to be determined using bus-specific

information. If the Error bit is 0, the PRD specified a smaller buffer size than the

programmed IDE transfer size.

Bit Description

31:2 Descriptor Table Base Address (DTBA). Bits [31:2] correspond to A[31:2].

1:0 Reserved.