SM Bus Controller Configuration

14-4 Intel® 460GX Chipset Software Developer’s Manual

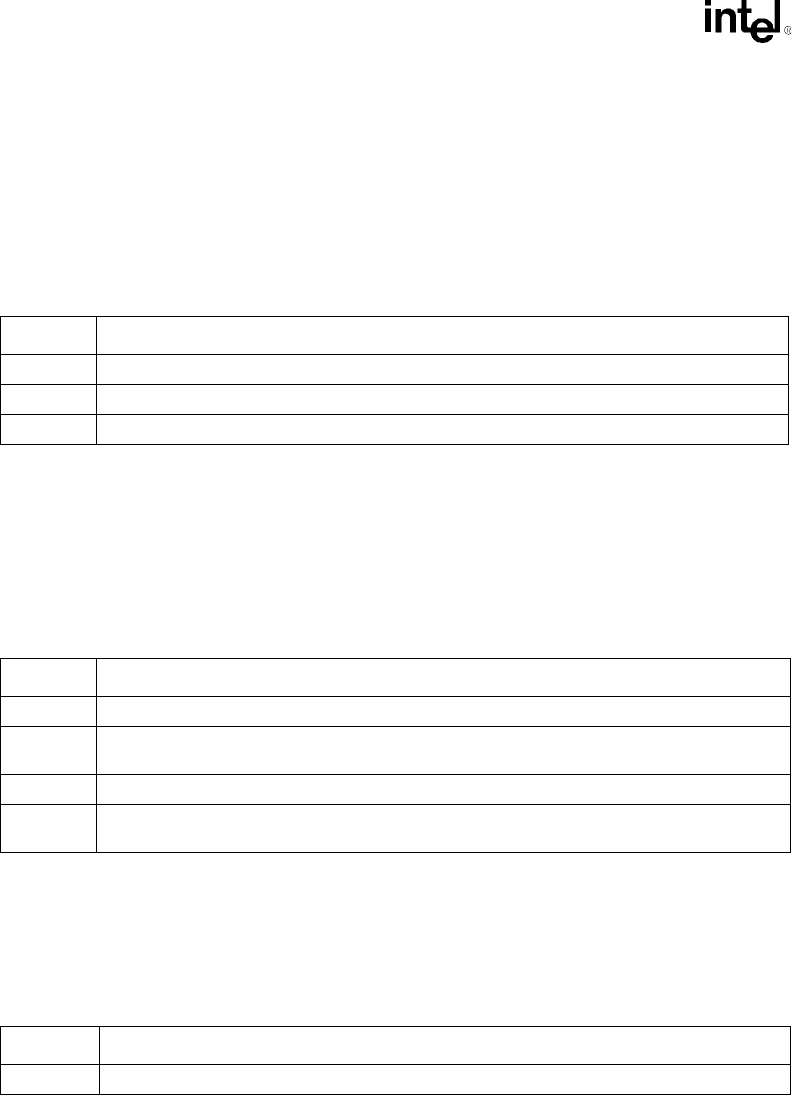

14.2.6 CLASSC–Class Code Register (Function 3)

Address Offset: 09-0Bh

Default Value: 0C0500h

Attribute: Read only

This register identifies the Base Class Code, Sub-Class Code, and Device Programming interface

for IFB PCI Function 3.

14.2.7 SMBBA–SMBus Base Address (Function 3)

Address Offset: 20-23h

Default Value: 00000001h

Attribute: Read/Write

This register contains the base address of the SMBus I/O Registers.

14.2.8 SVID–Subsystem Vendor ID (Function 3)

Address: 2C-2Dh

Default Value: 0000h

Attribute: Read only

Bit Description

23:16 Base Class Code (BASEC). 0Ch = Serial Bus Controller.

15:8 Sub-Class Code (SCC). 05h = System Management Bus (SMBus) Controller.

7:0 Programming Interface (PI). 00h = No specific register level programming defined.

Bit Description

31:16 Reserved. Hardwired to 0s. Must be written as 0s.

15:4 Index Register Base Address. Bits [15:4] correspond to I/O address signals AD [15:4],

respectively.

3:1 Reserved. Read as 0.

0 Resource Type Indicator (RTE)–RO. This bit is hardwired to 1 indicating that the base address

field in this register maps to I/O space.

Bit Description

15:0 Subsystem Vendor ID.