LPC/FWH Interface Configuration

11-24 Intel® 460GX Chipset Software Developer’s Manual

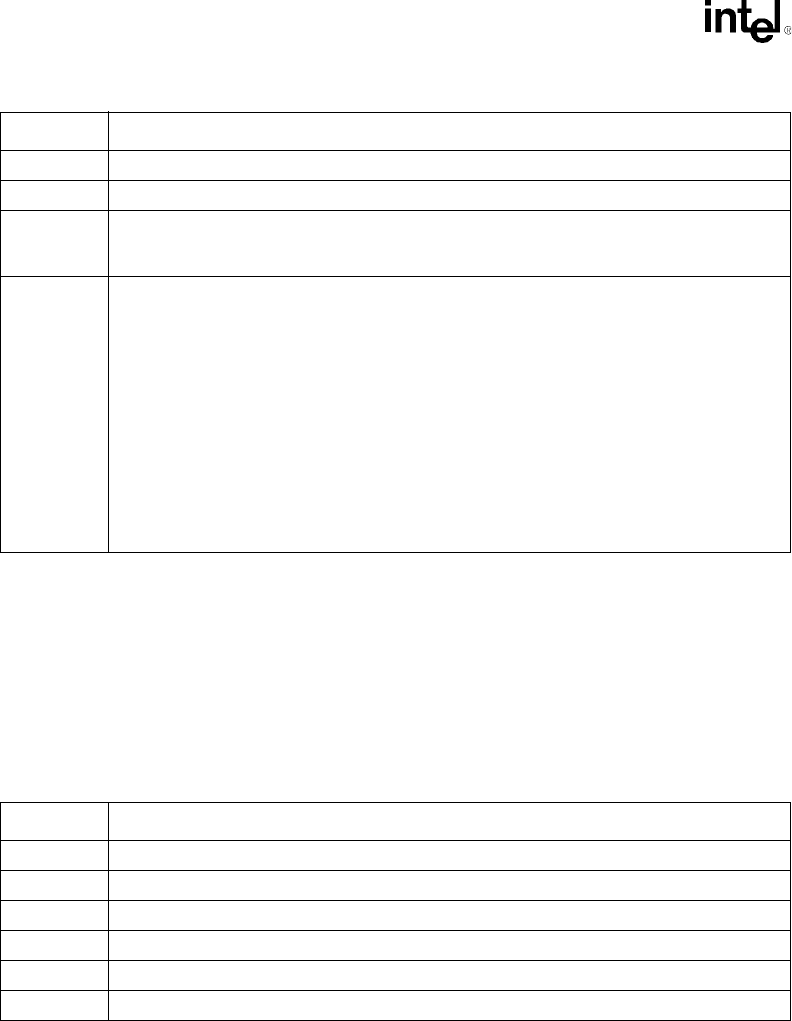

11.2.2.9 Elcr1–Edge/Level Control Register (I/O)

I/O Address: INT CNTRL-1–4D0h

Default Value: 00h

Attribute: Read/Write

ELCR1 register allows IRQ3 - IRQ7 to be edge or level programmable on an interrupt by interrupt

basis. IRQ0, IRQ1 and IRQ2 are not programmable and are always edge sensitive. When level

triggered, the interrupt is signaled active when input IRQ signal is high.

5 Enable Special Mask Mode (ESMM). 1=Enable SMM bit; 0=Disable SMM bit.

4:3 OCW3 Select. Must be programmed to 01 selecting OCW3.

2 Poll Mode Command. 0=Disable Poll Mode Command. When bit 2=1, the next I/O read to the

interrupt controller is treated as an interrupt acknowledge cycle indicating highest priority

request.

1:0 Register Read Command. Bits [1:0] provide control for reading the In-Service Register (ISR)

and the Interrupt Request Register (IRR). When bit 1=0, bit 0 does not affect the register read

selection. When bit 1=1, bit 0 selects the register status returned following an OCW3 read. If bit

0=0, the IRR will be read. If bit 0=1, the ISR will be read. Following ICW initialization, the

default OCW3 port address read will be “read IRR”. To retain the current selection (read ISR or

read IRR), always write a 0 to bit 1 when programming this register. The selected register can

be read repeatedly without reprogramming OCW3. To select a new status register, OCW3

must be reprogrammed prior to attempting the read.

Bit[1:0] Function

00 No Action

01 No Action

10 Read IRQ Register

11 Read IS Register

Bit Description

Bit Description

7 IRQ7 ECL. 0 = Edge Triggered mode; 1 = Level Triggered mode.

6 IRQ6 ECL. 0 = Edge Triggered mode; 1 = Level Triggered mode.

5 IRQ5 ECL. 0 = Edge Triggered mode; 1 = Level Triggered mode.

4 IRQ4 ECL. 0 = Edge Triggered mode; 1 = Level Triggered mode.

3 IRQ3 ECL. 0 = Edge Triggered mode; 1 = Level Triggered mode.

2:0 Reserved. Must be 0.