Intel® 460GX Chipset Software Developer’s Manual 13-3

Universal Serial Bus (USB) Configuration

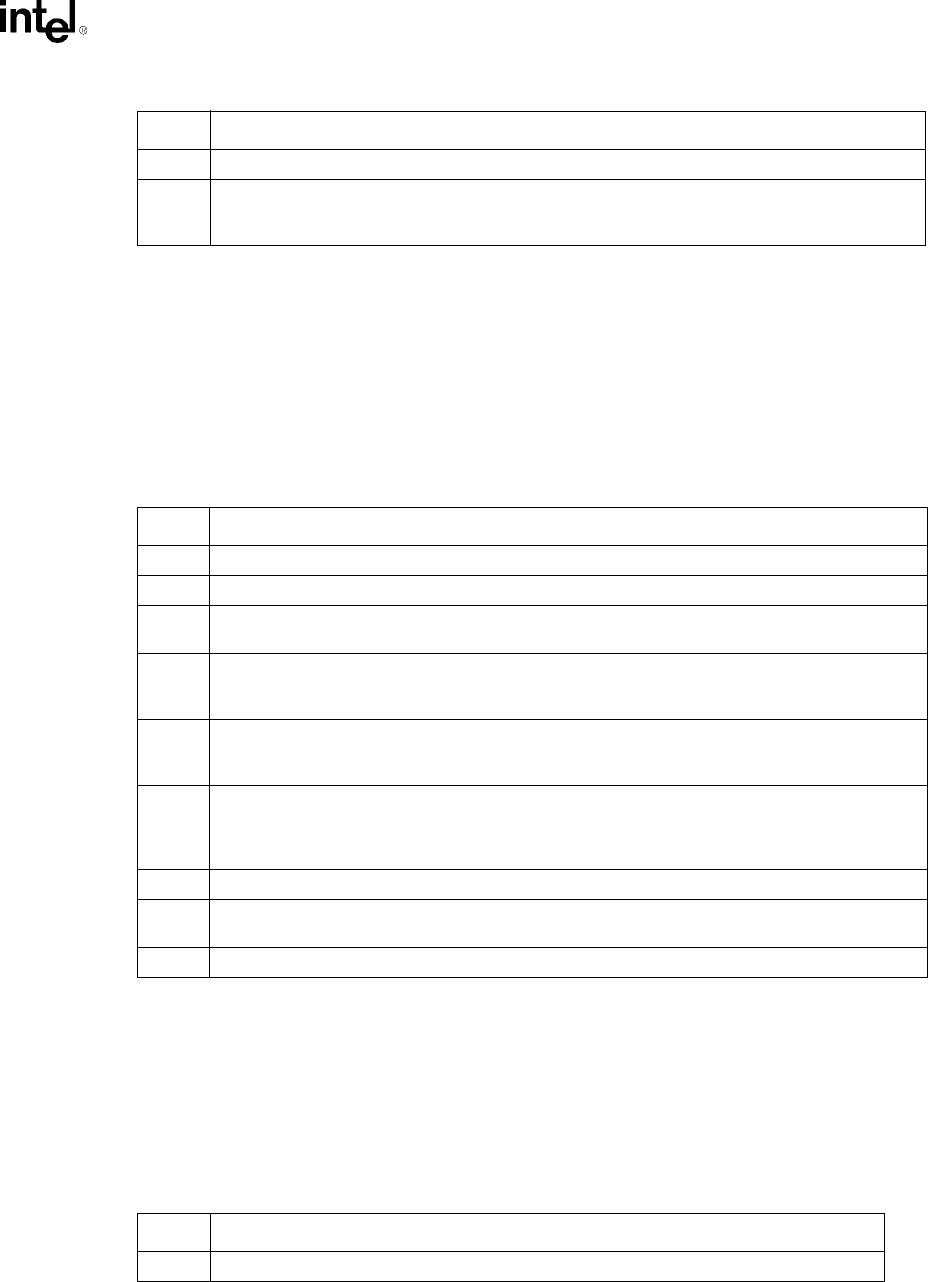

13.2.4 PCISTS–PCI Device Status Register (Function 2)

Address Offset: 06-07h

Default Value: 0280h

Attribute: Read/Write

DSR is a 16-bit status register that reports the occurrence of a PCI master-abort by the USB HC

module or a PCI target-abort when the Serial Bus module is a master. The register also indicates the

USB HC module DEVSEL# signal timing that is hardwired in the USB HC module.

13.2.5 RID–Revision Identification Register (Function 2)

Address Offset: 08h

Default Value: Initial Stepping = 00h. Refer to IFB Specification Updates

for other values programmed here.

Attribute: Read only

This 8 bit register contains device stepping information. Writes to this register have no effect.

1 Memory Space Enable (Not Implemented). This bit is hardwired to 0.

0 I/O Space Enable (IOSE). 1=Enable. 0=Disable. This bit controls the access to the I/O space

registers. If this bit is set, access to the host controller I/O registers is enabled. The base register for

the I/O registers must be programmed before this bit is set.

Bit Description

Bit Description

15 Detected Parity (Not Implemented). Read as 0.

14 SERR# Status (Not Implemented). Read as 0.

13 Master-Abort Status (MAS)–R/WC. When the Serial Bus module receives a master-abort from a

PCI transaction, MAS is set to a 1. Software sets MAS to 0 by writing a 1 to this bit.

12 Received Target-Abort Status (RTA)–R/WC. When the Serial Bus module is a master on the PCI

Bus and receives a target-abort, this bit is set to a 1. Software resets RTA to 0 by writing a 1 to this

bit.

11 Signaled Target-Abort Status (STA)–R/WC. This bit is set when the Serial Bus module Function is

targeted with a transaction that the Serial Bus module terminates with a target abort. Software

resets STA to 0 by writing a 1 to this bit.

10:9 DEVSEL# Timing Status (DEVT)–RO. This 2-bit field defines the timing for DEVSEL# assertion.

These read only bits indicate the IFB’s DEVSEL# timing when performing a positive decode. Since

the IFB always generate the DEVSEL# with medium timing, DEVT=01. This DEVSEL# timing does

not include Configuration cycles.

8 Data Parity Detected (Not Implemented). Read as 0.

7 Fast Back to Back Capable (FBC)–RO. Hardwired to 1. This bit indicates to the PCI Master that

Serial Bus module as a target is capable of accepting fast back-to-back transactions.

6:0 Reserved. Read as 0’s.

Bit Description

7:0 Revision ID Byte. The register is hardwired to the default value.