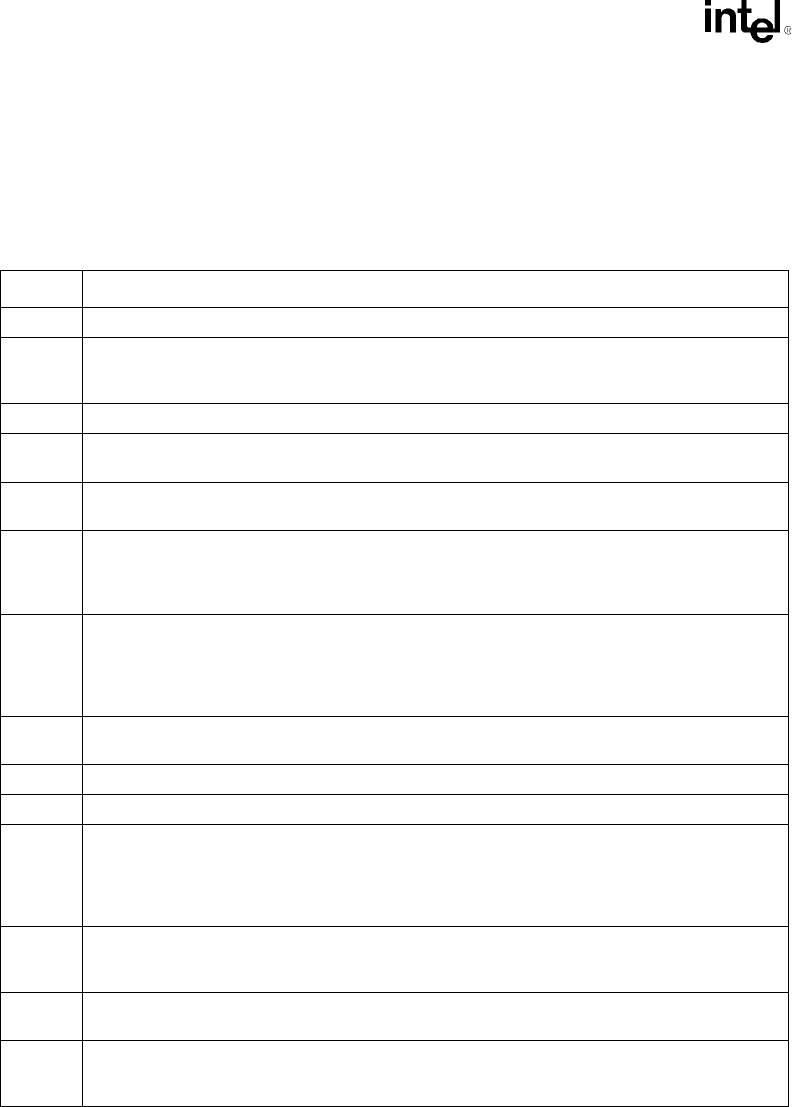

LPC/FWH Interface Configuration

11-36 Intel® 460GX Chipset Software Developer’s Manual

11.2.8.1 Global Control and Enable

Address Offset: 1A-1Bh

Attributes: Read/Write

Default Value: Bits 8 Undefined, Bit 3 ‘1’, All other bits ‘0’

Size: 16 bits

Bit Description

15:13 Reserved.

12 ACPI_TMR_EN: If not using ACPI (SCI) mode, as indicated by SCI_EN not set, then the

ACPI_TMR_EN bit can be set to cause an SMI#. SMI will be generated if this bit, SMI_EN and

TMROF_EN are set, and SCI_EN is not set.

11 Reserved.

10 APMC_EN: Software sets this bit to 1 to enable SMIs based upon accesses to the APM control

port at B2h in I/O space.

9 ECC_EN: This bit is used to enable the generation of SMI when the ECC_STS bit in the Global

Status Register is set.

8 EXTSMI_EN: This bit is used to enable the setting of the EXTSMI_STS bit to generate an SMI

event (SMI# or Wake/Break). The EXTSMI_STS bit is set anytime a GPIO is programmed as an

input, is routed to generate an SMI#, and has its register bit set. Upon power up, this bit is

undefined.

7 SWSMI_TMR_EN: Software sets this bit to a 1 to start the Software SMI# Timer. When the 128

ms timer expires (±4.57 ms), it will generate an SMI# and set the SWSMI_TMR_STS bit. The

SWSMI_TMR_EN bit will remain at 1 until software sets it back to 0. Once the timer has been

started, if SWSMI_TMR_EN bit is set to 0 before the timer expires, the timer will not expire, and

the SMI# will not be generated. The default for this bit is 0.

6 1MIN_EN: Enables the 1 minute timer (±1.17s) to count. When it reaches its timeout, it will

generate an SMI#.

5 Reserved.

4 BIOS_EN: Enables the generation of SMI# when ACPI software writes a 1 to the GBL_RLS bit.

3 EOS: End of SMI. This bit controls the arbitration of the SMI signal to the processor. When this bit

is set, SMI# will be deasserted. Also this bit will be automatically cleared once IFB asserts SMI#

low. In the SMI handler, the processor should clear all pending SMIs (by servicing them and then

clearing their respective status bits) and then setting this bit and resuming. This will allow the SMI

arbiter to re-assert SMI upon detection of an SMI event and the setting of a SMI status bit.

2 THRM_POL: This bit controls the polarity of the THRM# pin needed to set the THRM_STS bit.

When the THRM_POL bit is LOW then a HIGH value on the THRM# signal will set the

THRM_STS bit.

1 BIOS_RLS: Enables the generation of an SCI interrupt for ACPI software when a one is written to

this bit position by firmware software. This bit always reads a zero.

0 SMI_EN: When set, this bit enables the generation of SMIs in the system upon any enabled SMI

event. The exception is when the BIOS Write Enable bit of the BOISEN register is set, an SMI is

generated regardless of the state of the SMI_EN bit. This bit is reset by a PCI reset event.