PCI/LPC Bridge Description

15-16 Intel® 460GX Chipset Software Developer’s Manual

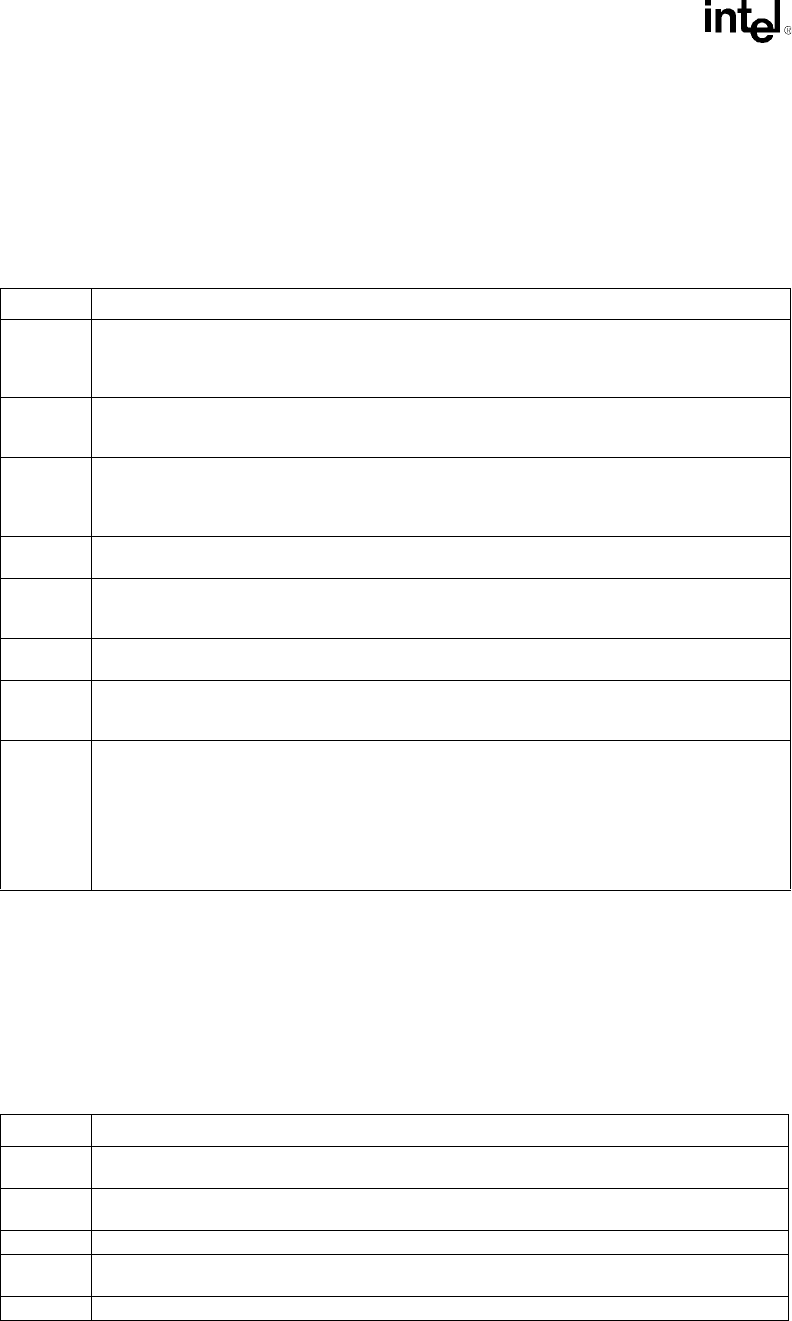

15.5.1.2 Register B

Address Offset: 0Bh

Default Value: X0000XXXb

Attribute: Read/Write

This register is used for general configuration of the RTC Functions.

15.5.1.3 Register C

Address Offset: 0Ch

Default Value: 00h

Attribute: Read/Write

This register is used for various flags. All flag bits are cleared upon active RSMRST# or a read of

Register C.

Bit(s) Description

7 SET: Enables the update cycles. When is zero, update cycle occurs normally once a second. If

set to one, a current update cycle will abort and subsequent update cycles will not occur until SET

is returned to zero. When set is one, the firmware may initialize time and calendar bytes safely.

This bit is not affected by RSMRST#.

6 Periodic Interrupt Enable (PIE): If set to one, the Periodic Interrupt Enable (PIE) bit allows an

interrupt to occur with a time base set with the RS bits of register A. This bit is cleared (set to

zero) on active RSMRST#.

5 Alarm Interrupt Enable (AIE): If set to one, the Alarm Interrupt Enable (AIE) bit allows an

interrupt to occur when the AF is one as set from an alarm match from the update cycle. An alarm

can occur once a second, one an hour, once a day, or one a month. This bit is cleared on active

RSMRST#.

4 Update-ended Interrupt Enable (UIE): If set to one, the Update-ended Interrupt Enable (UIE) bit

allows an interrupt to occur when the update cycle ends. This bit is cleared on active RSMRST#.

3 Square Wave Enable (SQWE): The Square Wave Enable bit serves no Function in this device,

yet is left in this register bank to provide compatibility with the Motorola 146818B. There is not

SQW pin on this device. This bit is cleared on active RSMRST#.

2 Data Mode (DM): The Data Mode (DM) bit specifies either binary or BCD data representation. A

one denotes binary, and zero denotes BCD. This bit is not affected by RSMRST#.

1 Hour Format (HF): This bit indicates the hour byte format. If one, twenty-four hour mode is

selected. If zero, twelve-hour mode is selected. In twelve hour mode, the seventh bit represents

AM as zero and PM as one. This bit is not affected by RSMRST#.

0 Daylight Savings Enable (DSE): The Daylight Savings Enable bit triggers two special hour

updates per year when set to one. One is on the first Sunday in April, where time increments from

1:59:59 AM to 3:00:00 AM. The other is the last Sunday in October when the time first reaches

1:59:59 AM, it is changed to 1:00:00 AM. The time must increment normally for at least two

update cycles (seconds) previous to these conditions for the time change to occur properly.

These special update conditions do not occur when the DSE bit is set to zero. The days for the

hour adjustment are those specified in United States federal law as of 1987, which is different

than previous years. This bit is not affected by RSMRST#.

Bit(s) Description

7 Interrupt Request Flag (IRQF): Interrupt Request Flag = PF * PIE + AF * AIE + UF *UFE. This

also causes the CH_IRQ_B signal to be asserted.

6 Periodic Interrupt Flag (PF): Periodic interrupt Flag will be one when the tap as specified by the

RS bits of register A is one. If no taps are specified, this flag bit will remain at zero.

5 Alarm Flag (AF): Alarm Flag will be high after all Alarm values match the current time.

4 Update-ended Flag (UF): Updated-ended flag will be high immediately following an update cycle

for each second.

3:0 Reserved. Read as 0.