Universal Serial Bus (USB) Configuration

13-10 Intel® 460GX Chipset Software Developer’s Manual

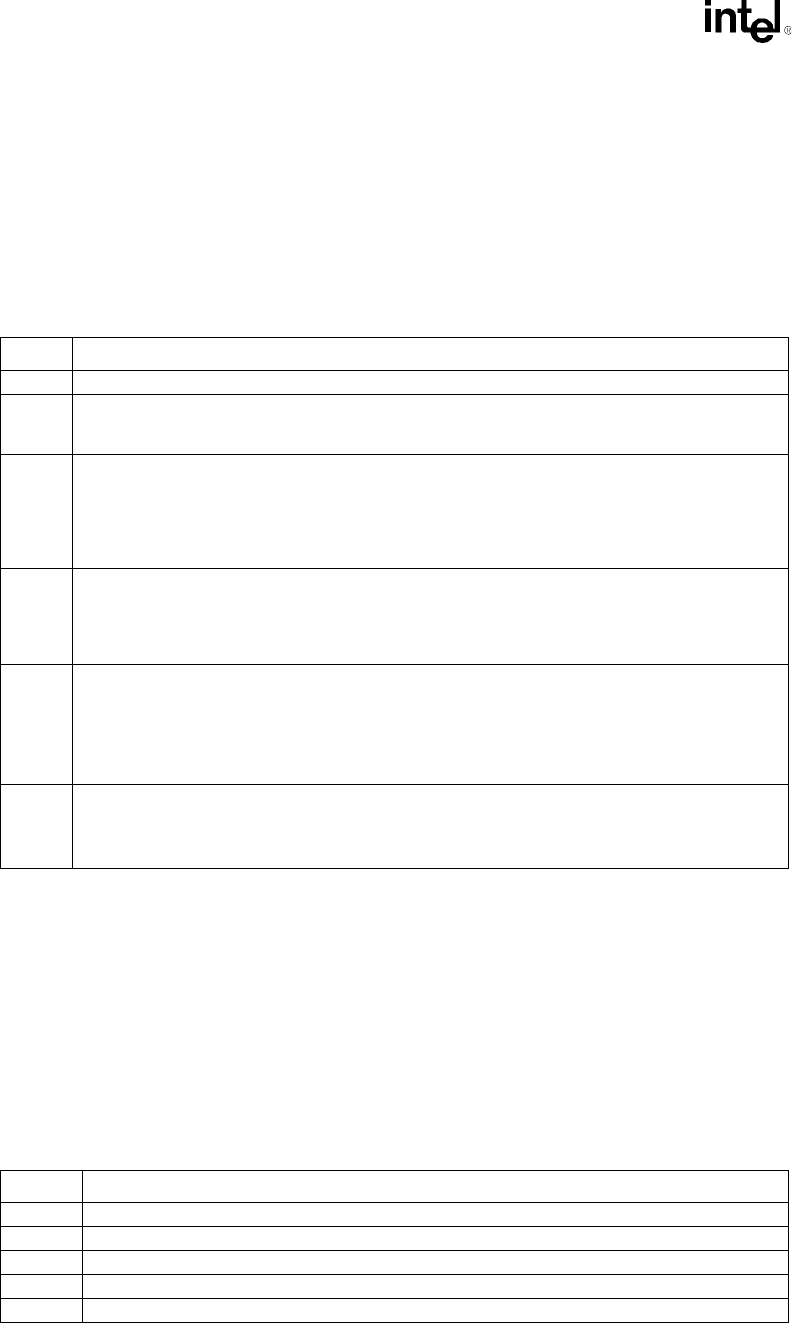

13.3.2 USBSTS–USB Status Register (I/O)

I/O Address: Base + (02-03h)

Default Value: 0000h

Attribute: Read/Write Clear

This register indicates pending interrupts and various states of the Host Controller. The status

resulting from a transaction on the serial bus is not indicated in this register. Software sets a bit to 0

in this register by writing a 1 to it.

13.3.3 USBINTR–USB Interrupt Enable Register (I/O)

I/O Address: Base + (04-05h)

Default Value: 0000h

Attribute: Read/Write

This register enables and disables reporting of the corresponding interrupt to the software. When a

bit is set and the corresponding interrupt is active, an interrupt is generated to the host. Fatal errors

(Host Controller Processor Error- bit 4, USBSTS Register) cannot be disabled by the host

controller. Interrupt sources that are disabled in this register still appear in the Status Register to

allow the software to poll for events.

Bit Description

15:6 Reserved.

5 HCHalted. The Host Controller sets this bit to 1 after it has stopped executing as a result of the

Run/Stop bit being set to 0, either by software or by the Host Controller hardware (debug mode or

an internal error).

4 Host Controller Process Error. The Host Controller sets this bit to 1 when it detects a fatal error

and indicates that the Host Controller suffered a consistency check failure while processing a

Transfer Descriptor. An example of a consistency check failure would be finding an illegal PID field

while processing the packet header portion of the TD. When this error occurs, the Host Controller

clears the Run/Stop bit in the Command register to prevent further schedule execution. A hardware

interrupt is generated to the system.

3 Host System Error. The Host Controller sets this bit to 1 when a serious error occurs during a host

system access involving the Host Controller module. In a PCI system, conditions that set this bit to

1 include PCI Parity error, PCI Master Abort, and PCI Target Abort. When this error occurs, the Host

Controller clears the Run/Stop bit in the Command register to prevent further execution of the

scheduled TDs. A hardware interrupt is generated to the system.

2 Resume Detect. The Host Controller sets this bit to 1 when it receives a “RESUME” signal from a

USB device. This is only valid if the Host Controller is in a global suspend state (bit 3 of Command

register = 1).

1 USB Error Interrupt. The Host Controller sets this bit to 1 when completion of a USB transaction

results in an error condition (e.g. error counter underflow). If the TD on which the error interrupt

occurred also had its IOC bit set, both this bit and Bit 0 are set.

0 USB Interrupt (USBINT). The Host Controller sets this bit to 1 when the cause of an interrupt is a

completion of a USB transaction whose Transfer Descriptor had its IOC bit set.

The Host Controller also sets this bit to 1 when a short packet is detected (actual length field in TD

is less than maximum length field in TD), and short packet detection is enabled in that TD.

Bit Description

15:4 Reserved.

3 Short Packet Interrupt Enable. 1=Enabled. 0=Disabled.

2 Interrupt On Complete (IOC) Enable. 1= Enabled. 0=Disabled.

1 Resume Interrupt Enable. 1= Enabled. 0=Disabled.

0 Time-out/CRC Interrupt Enable. 1= Enabled. 0=Disabled.