SILICON GATE MOS

8302

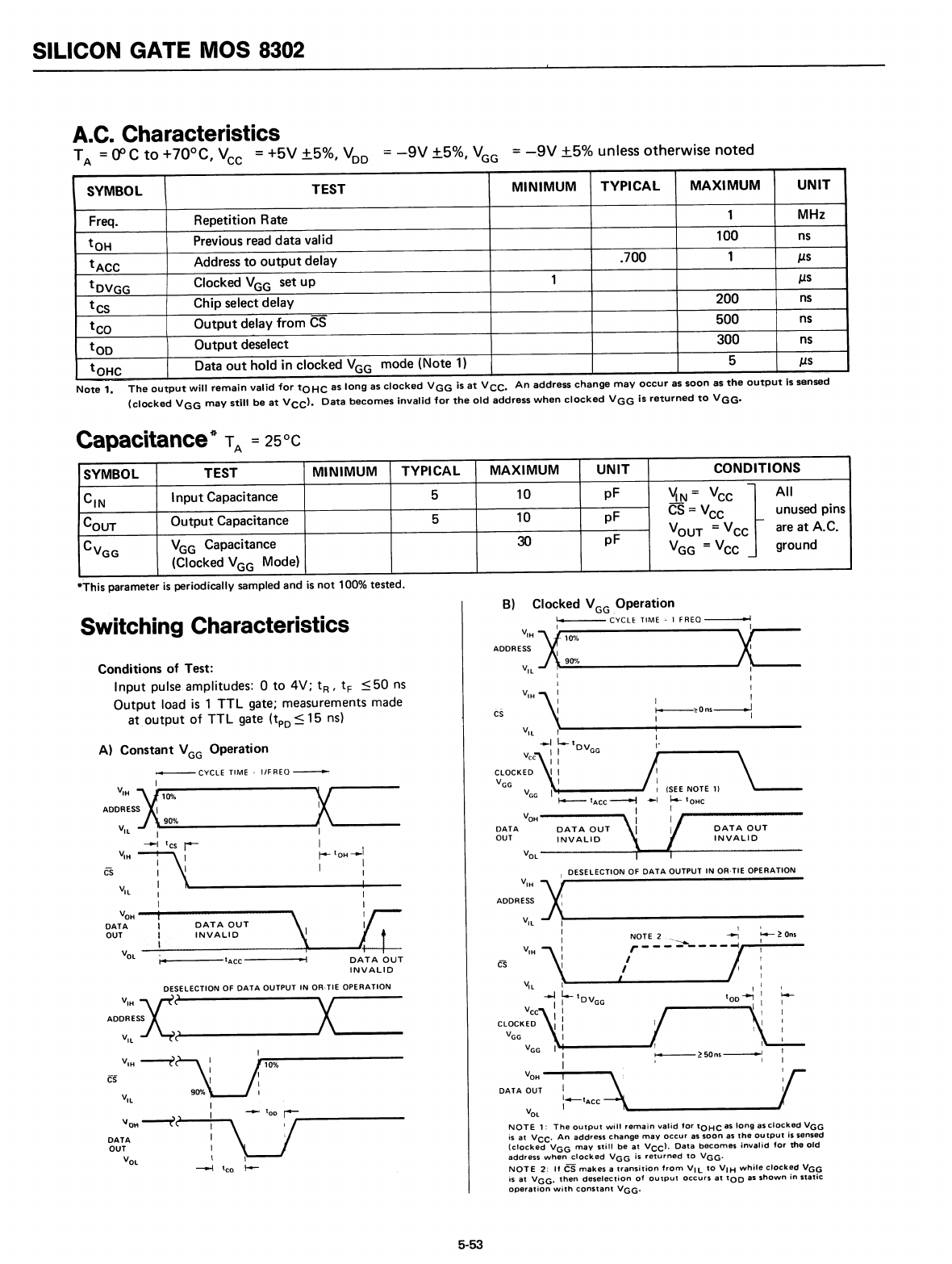

A.C. Characteristics

TA =

(1J

C

to

+

70°C,

Vee

=+5V ±5%, V

oo

=

-9V

±5%, V

GG

=

-9V

±5% unless otherwise noted

SYMBOL

TEST

MINIMUM

TYPICAL

MAXIMUM

UNIT

Freq.

Repetition

Rate

1

MHz

tOH

Previous read

data

valid

100

ns

tACC

Address

to

output

delay

.700

1

JJ.s

t

ovGG

Clocked V

GG

set

up

1

JJ.s

t

cs

Chip

select

delay

200

ns

tco

Output

delay

from

CS

500

ns

too

Output

deselect

300

ns

t

OHC

Data

out

hold

in

clocked

V

GG

mode

(Note

1)

5

JJ.s

Note

1.

The

output

will

remain

valid

for

tOHC

as

long

as

clocked

VGG

is

at

Vce.

An

address

change

may

occur

as

soon

as

the

output

is

sensed

(clocked

VGG

may

still

be

at

Vee).

Data

becomes

invalid

for

the

old

address

when

clocked

VGG

is

returned

to

VGG.

Capacitance* T

A

= 25°C

SYMBOL

TEST

MINIMUM TYPICAL MAXIMUM

UNIT

CONDITIONS

C

,N

I

nput

Capacitance

5

10

pF

"1N=

vee}

All

C

OUT

Output

Capacitance

5

10

pF

CS =V

CC

unused

pins

C

VGG

V

GG

Capacitance

30

pF

V

OUT

=V

CC

are

at

A.C.

(Clocked

VGGMode)

V

GG

=V

CC

ground

*This parameter

is

periodically sampled

and

is

not

100%

tested.

A)

Constant

V

GG

Operation

Switching

Characteristics

DATA

OUT

INVALID

DATA

OUT

INVALID

VOH-----~

DATA

OUT

V

,H

-v.

DESELECTlDN OF DATA OUTPUT

IN

OR·TlE OPERATION

ADDRESS

.fi.

V

1L

1-----------------

: NOTE 2 . _

~

~

~

Ons

cs

V

,H

~

,',r---~----l

...

·

......

i---

'-"L

I

,I

I

~

"-

to

too

--,

I

~

v

cc

,,:

: V

GG

L

'

::

CLOCKED

I:

III

I I

V

GG

I I I

V

GG

1-+1-----....",

I I

I

...--~50ns---1

I

I I I I

V

{I:

DATA

O~HT

i-'ACC

~

.

VOL

......

----------1

VOL

---------r--ISr----------

NOTE

1:

The

output

will

remain

valid

for

tOHe

as

long

as

clocked

VGG

is

at

Vee.

An

address

change

may

occur

as

soon

as

the

output

is

sensed

(clocked

VGG

may

still

be

at

Vee).

Data

becomes

invalid

for

the

old

address

when

clocked

VGG

is

returned

to

VGG'

NOTE

2:

If

CS

makes

a

transition

from

VI

L

to

VIH

while

clocked

VGG

is

at

VGG,

then

deselection

of

output

occurs

at

too

as

shown

in

static

operation

with

constant

VGG'

B)

Clocked V

GG

Operation

~

CYCLE

TIME

~

I

FREO---....l

ADDRE~~H

~

::

>C

V

1L

I I

I I

I

V

IH

,,:

I I

CS

'\

~~ons---{

V

1L

I I

_I

~tDV

:.

Vee,;

:

GG

/:..--------..\

CLOCKED

'\

I / ;

V

GG

V

GG

I':

:(SEE

NOTE

1)

~---

.-.-

'ACC

~

--I

~

t

OHC

I I

I I

I I

DATA

OUT

INVALID

....

1·----tAcc-----·~1

V

1H

---f

10%

CS

V

1L

1

"o~---f()

1

- too

~

I

U

DATA

I

OUT

I

VOL

I

I

---l

t

co

.-

--CYCLE

TIME'

I/FREO-

V

,----------_

IH

V

10

% V

ADDRESSfi

90%

A

V

1L

1 I

~----

--I

'cs

~

I

_ V

1H

n'

t--

t

oH

--l

cs I I

I:

V

1L

: :

I I

g~~~H

--4!~--~N-~-TA-AL-~-DU-T--~\

r;-

VOL

t---+--

DESELECTION OF

DATA

OUTPUT

IN

OR·TlE

OPERATION

AD:~:Y::

X"----

VIL'~

Conditions

of

Test:

Input

pulse.amplitudes: 0

to

4V;

t

R

,

t

F

~

50

ns

Output

load

is

1

TTL

gate;

measurements

made

at.

output

of

TTL

gate (t

pD

::5

15

ns)

5-53