Silicon Gate MOS 8101-2

1024

BIT

(256

x

4)

STATIC MOS RAM

WITH SEPARATE

1/0

•

256

x 4 Organization

to

Meet Needs

for Small System Memories

• Access Time -

850 nsec Max.

• Single

+

5V

Supply Voltage

• Directly TTL Compatible - All Inputs

and Output

• Static MOS - No Clocks

or

Refreshing Required

• Simple Memory Expansion - Chip

Enable Input

• Inputs Protected -

All

Inputs Have

Protection Against Static Charge

• Low Cost Packaging -

22

Pin Plastic

Dual-In-Line Configuration

• Low Power - Typically 150 mW

• Three-State Output - OR-Tie

Capability

• Output Disable Provided

for

Ease

of

Use in Common Data Bus Systems

®

The Intel 8101-2

is

a 256

word

by

4

bit

static random

access

memory element using

normally

off

N-channel

MOS

devices integrated on a

monolithic

array.

It

uses

fully

DC

stable (static)

circuitry

and therefore requires

no clocks

or

refreshing

to

operate. The data

is

read

out

nondestructively and

has

the

same

polarity

as

the

input

data.

The 8101-2

is

designed

for

memory applications where high performance,

low

cost, large

bit

storage, and sim-

ple interfacing

are

important

design objectives.

It

is

directly

TTL

compatible in all respects: inputs, outputs, and a single

+5V

supply.

Two

chip-enables

allow

easy

selection

of

an

individual package when

outputs

are OR-tied.

An

output

disable

is

provided

so

that

data inputs and

outputs

can

be

tied

for

common

I/O

systems.

Output

disable

is

then

used

to

eliminate

any

bidirectional logic.

®

The Intel 8101-2

is

fabricated

with

N-channel silicon gate technology. This technology allows the design

and_

production

of

high performance, easy-to-use MOS circuits and provides a higher

functional

density on a mon-

olithic

chip than either conventional MOS technology

or

P-channel silicon gate technology.

Intel's silicon gate technology also provides excellent protection against contamination. This permits

the

use

of

low

cost silicone packaging.

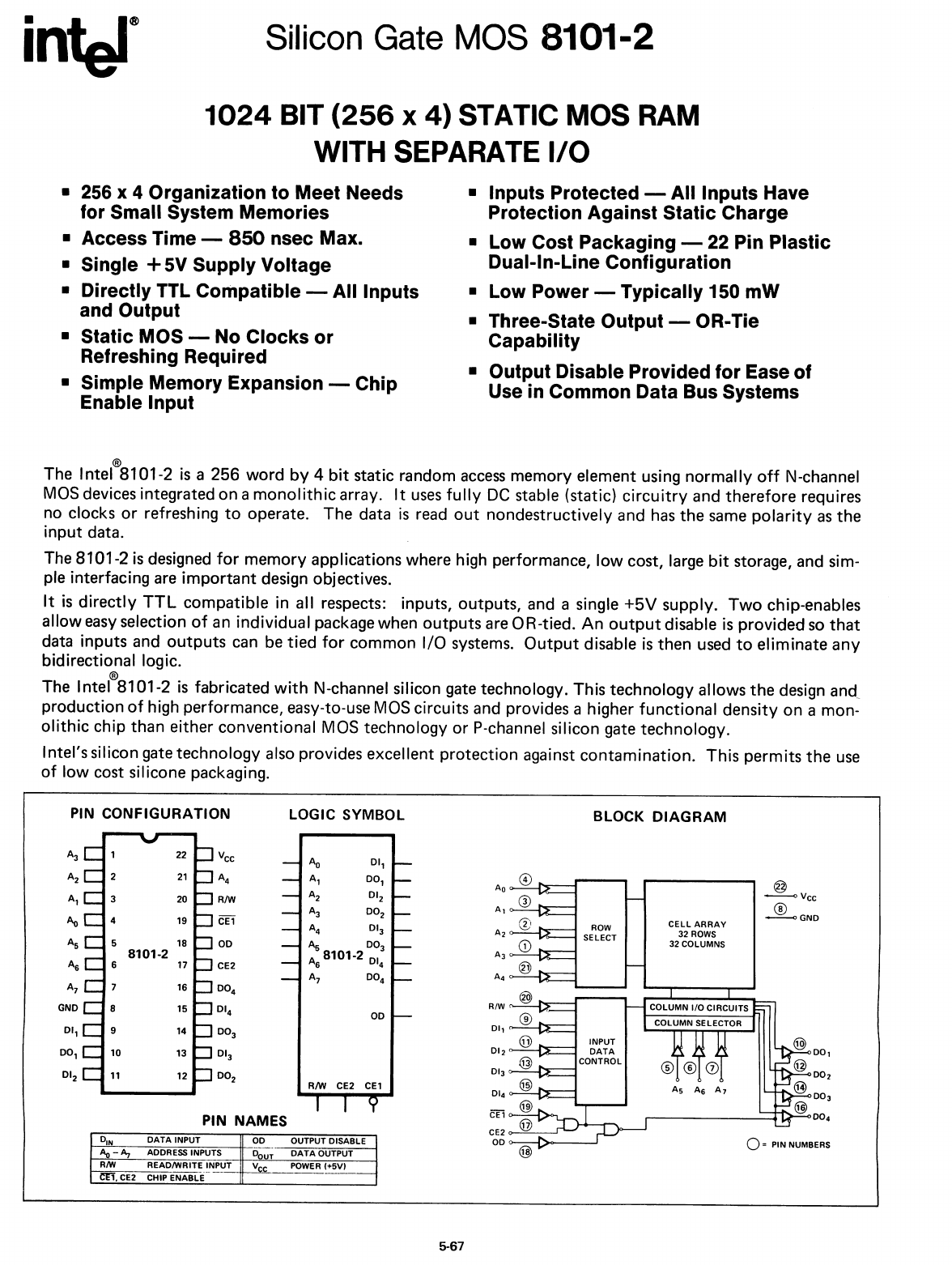

@

---0

Vee

~GND

o =PIN NUMBERS

CELL

ARRAY

32

ROWS

32

COLUMNS

ROW

SELECT

AO

BLOCK

DIAGRAM

m~-.~

CE2~---I

00

::>--4

>o-~

R/W

DIN

DATA

INPUT

00

OUTPUT

DISABLE

Ao-A.,

ADDRESS INPUTS

D

OUT

DATA

OUTPUT

RIW

READIWRITE

INPUT

Vee

POWER (+5V)

m,CE2

CHIP

ENABLE-

PIN CONFIGURATION

LOGIC SYMBOL

A

3

22

Vee

A

o

01,

A

2

21

A

4

A,

DO,

A,

20

RIW

A

2

01

2

Ao

A

3

00

2

4 19

CEl

A

4

01

3

As

5

18

00

As

003

8101-2

A

6

8101-2

01

4

A

6

6

17

CE2

A

7

0°4

A

7

16

0°4

GNo

8

15

01

4

00

01,

9 14

0°3

DO,

10 13

01

3

01

2

11

12

0°2

RIW

CE2

CEl

PIN NAMES

5-67