Condition Flags:

There

are five

condition

flags associated

with

the

exe-

cution

of

instructions

on

the

8080.

They

are

Zero,

Sign,

Parity, Carry,

and

Aux

iIiary Carry,

and

are each represented

by a

l-bit

register

in

the

CPU. A flag

is

"set"

by forcing

the

bit

to

1; "reset" by forcing

the

bit

to

O.

Unless indicated otherwise,

when

an instruction af-

fects a flag, it affects it

in

the

following

manner:

Zero: If

the

result

of

an

instruction

has

the

value

0,

this

flag

is

set;

otherwise it

is

reset.

address

where

the

data

is

located

(the

high-order bits

of

the

address are

in

the

first register

of

the

pair,

the

low-order

bits

in

the

second).

• Immediate -

The

instruction

contains

the

data

it-

self. This

is

either

an

8-bit

quantity

or

a

16-bit

quantity

(least significant

byte

first,

most

significant

byte

second).

Unless directed by an

interrupt

or

branch

instruction,

the

execution

of

instructions

proceeds

through

consecu-

tively increasing

memory

locations. A branch instruction

can specify

the

address

of

the

next

instruction

to

be exe-

cuted

in

one

of

two

ways:

• Direct -

The

branch

instruction

contains

the

ad-

dress

of

the

next

instruction

to

be exe-

cuted.

(Except

for

the

'RST'

instruction,

byte

2

contains

the

low-order address

and

byte

3

the

high-order address.)

• Register indirect -

The

branch

instruction

indi-

cates a register-pair which

contains

the

address

of

the

next

instruction

to

be exe-

cuted.

(The

high-order

bits

of

the

address

are

in

the

first register

of

the

pair,

the

low-order bits

in

the

second.)

The

RST instruction

is

a special

one-byte

call instruc-

tion

(usually used during

interrupt

sequences). RST in-

cludes a

three-bit

field; program

control

is

transferred

to

the

instruction whose address

is

eight

times

the

contents

of

this

three-bit

field.

The

8080

can

directly

address

up

to

65,536

bytes

of

mem-

ory, which may

consist

of

both

read-only

memory

(ROM)

elements and random-access

memory

(RAM)

elements

(read/

write

memory).

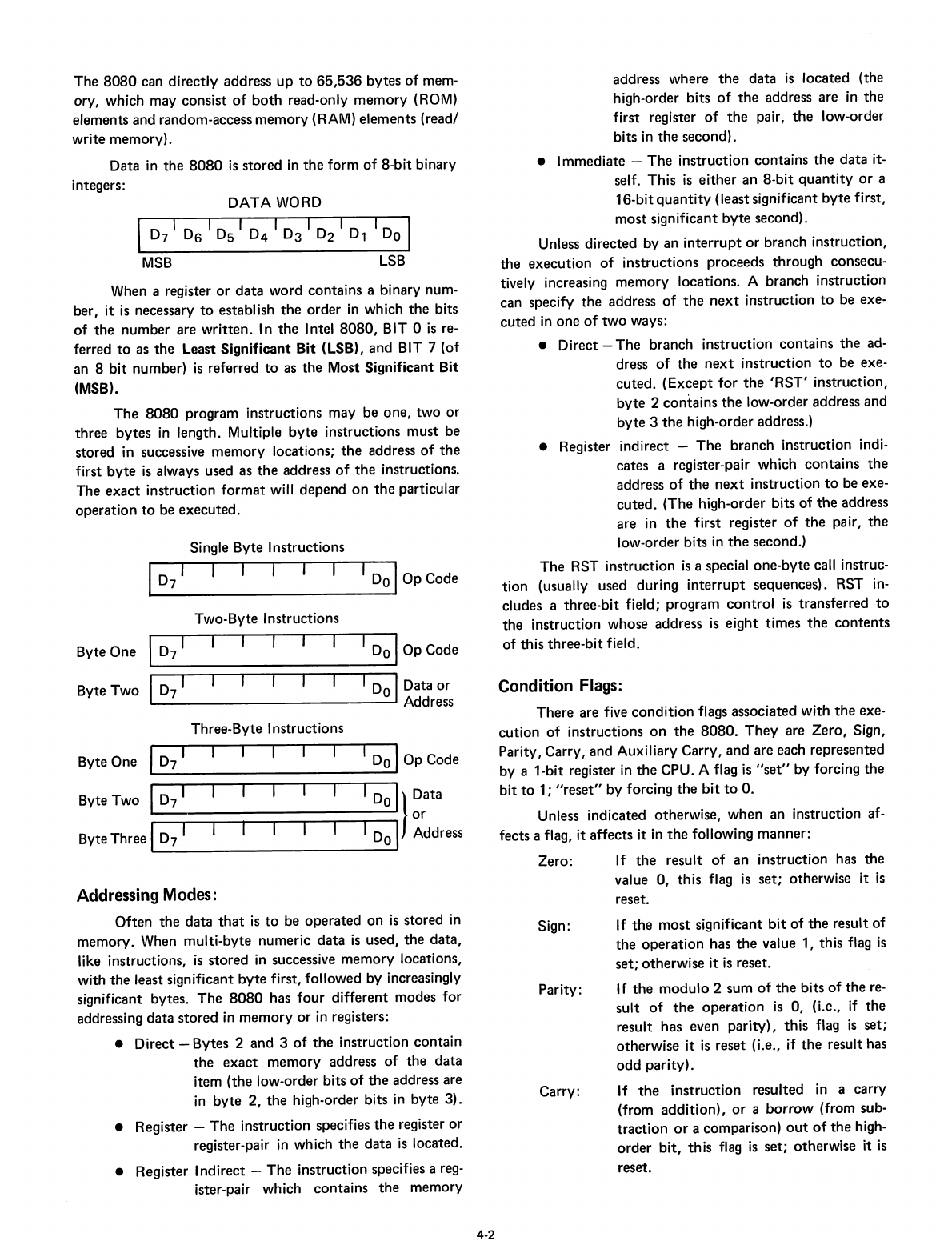

Oata

in

the

8080

is

stored

in

the

form

of

8-bit

binary

integers:

OATA

WORO

I

I 1 1 I 1 I I I

07

06

05

04 03

02

D1

00

MSB

LSB

When a register

or

data

word

contains

a binary num-

ber, it

is

necessary

to

establish

the

order

in

which

the

bits

of

the

number

are

written.

In

the

Intel

8080,

BIT 0

is

re-

ferred

to

as

the

Least Significant Bit (LSB),

and

BIT 7 (of

an 8

bit

number)

is

referred

to

as

the

Most Significant Bit

(MSB).

The

8080

program instructions

may

be

one,

two

or

three

bytes

in

length. Multiple

byte

instructions

must

be

stored in successive

memory

locations;

the

address

of

the

first

byte

is

always used as

the

address

of

the

instructions.

The

exact

instruction

format

will

depend

on

the

particular

operation

to

be executed.

Si

ngle Byte Instructions

Two-Byte Instructions

Byte One

1_

0

_7_'

' I

__

0.......J

o

I

Op

Code

Byte

Two

I

D7

I I Do IOata

or

-,

-------------,

Address

Three-Byte Instructions

Byte One

I_D_7_

1

1_

0

0

I

Op

Code

Byte Two

I

D7

1

I Do

I)

Oata

or

Byte Three ID7 I I Do I Address

Addressing Modes:

Often

the

data

that

is

to

be

operated

on

is

stored

in

memory.

When

multi-byte

numeric

data

is

used,

the

data,

like instructions,

is

stored

in

successive

memory

locations,

with

the

least significant

byte

first, followed by increasingly

significant bytes.

The

8080

has

four

different

modes for

addressing

data

stored

in

memory

or

in

registers:

• Oirect - Bytes 2

and

3

of

the

instruction

contain

the

exact

memory

address

of

the

data

item (the low-order bits

of

the

address are

in

byte

2,

the

high-order bits

in

byte

3).

• Register -

The

instruction specifies

the

register

or

register-pair

in

which

the

data

is

located.

• Register Indirect -

The

instruction specifies a reg-

ister-pair which

contains

the

memory

4-2

Sign:

Parity:

Carry:

If

the

most

significant

bit

of

the

result

of

the

operation

has

the

value 1, this flag

is

set;

otherwise

it

is

reset.

If

the

modulo

2 sum

of

the

bits

of

the

re-

sult

of

the

operation

is

0, (Le., if

the

result has even

parity),

this

flag

is

set;

otherwise

it

is

reset (Le., if

the

result has

odd

parity).

If

the

instruction

resulted in a carry

(from

addition),

or

a

borrow

(from sub-

traction

or

a comparison)

out

of

the

high-

order

bit,

th

is

flag

is

set; otherwise it

is

reset.