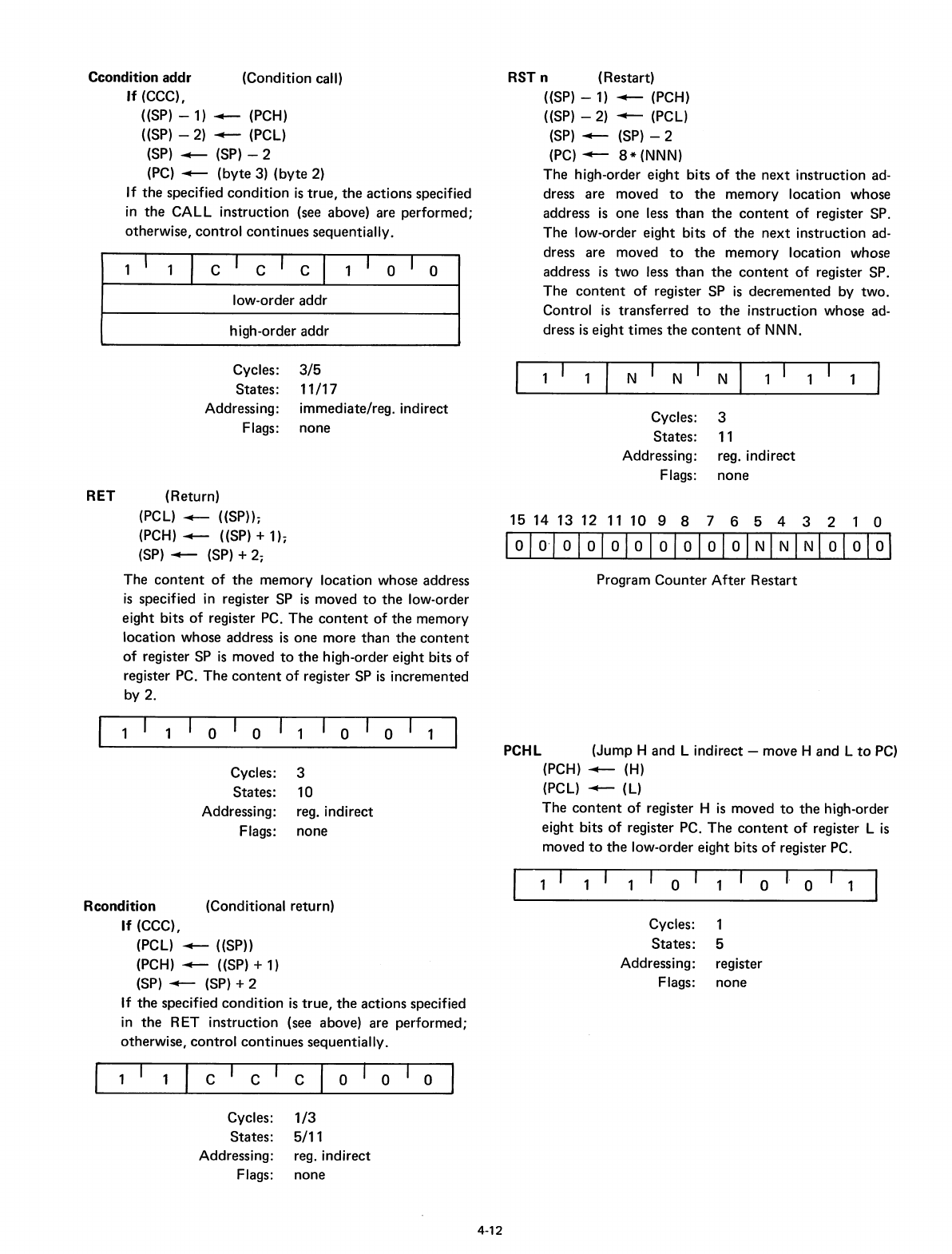

Ccondition addr

(Condition

call)

If

(CCC),

((SP)

-1)

~

(PCH)

((SP) -

2)

~

(PCl)

(SP)

~

(SP) - 2

(PC)

~

(byte

3)

(byte

2)

If

the

specified

condition

is

true,

the

actions

specified

in

the

CAll

instruction

(see above)

are

performed;

otherwise,

control

continues

sequentially.

1 '

1

I

C I

C I

c I

1

I

o I

0

low-order

addr

high-order

addr

RST

n

(Restart)

((SP) - 1)

~

(PCH)

((SP) -

2)

~

(PCl)

(SP)

~

(SP) - 2

(PC)

~

8*

(NNN)

The

high-order

eight

bits

of

the

next

instruction

ad-

dress

are

moved

to

the

memory

location

whose

address

is

one

less

than

the

content

of

register

SP.

The

low-order

eight

bits

of

the

next

instruction

ad-

dress

are

moved

to

the

memory

location

whose

address

is

two

less

than

the

content

of

register SP.

The

content

of

register

SP

is

decremented

by

two.

Control

is

transferred

to

the

instruction

whose

ad-

dress

is

eight

times

the

content

of

NNN.

Cycles:

States:

Addressing:

Flags:

Cycles:

States:

Addressing:

Flags:

3/5

11/17

immediate/reg.

indirect

none

1 I

N

N I

N I 1 I

3

11

reg.

indirect

none

RET

(Return)

(PCl)

~

((SP));

(PCH)

~

((SP) + 1);

(SP)

~

(SP) + 2;

The

content

of

the

memory

location

whose

address

is

specified

in register

SP

is

moved

to

the

low-order

eight

bits

of

register PC.

The

content

of

the

memory

location

whose

address

is

one

more

than

the

content

of

register SP

is

moved

to

the

high-order

eight

bits

of

register PC.

The

content

of

register SP

is

incremented

by

2.

Program

Counter

After

Restart

1 I

I 0 I 0

Cycles:

States:

Addressing:

Flags:

3

10

reg.

indirect

none

PCHL

(Jump

Hand

l

indirect

-

move

Hand

L

to

PC)

(PCH)

~

(H)

(PCl)

~

(l)

The

content

of

register H

is

moved

to

the

high-order

eight

bits

of

register PC.

The

content

of

register l

is

moved

to

the

low-order

eight

bits

of

register PC.

Rcondition

(Conditional

return)

If

(CCC),

(PCl)

~

((SP))

(PCH)

~

((SP) + 1)

(SP)

~

(SP)

+ 2

If

the

specified

condition

is

true,

the

actions

specified

in

the

RET

instruction

(see above)

are

performed;

otherwise,

control

continues

sequentially.

1 I 1 I

o '

Cycles:

States:

Addressing:

Flags:

o

,.

0 I 1

1

5

register

none

1 I

I c

c I c I 0 I 0 I 0

Cycles:

States:

Addressing:

Flags:

1/3

5/11

reg.

indirect

none

4-12