SILICON GATE MOS 8111-2

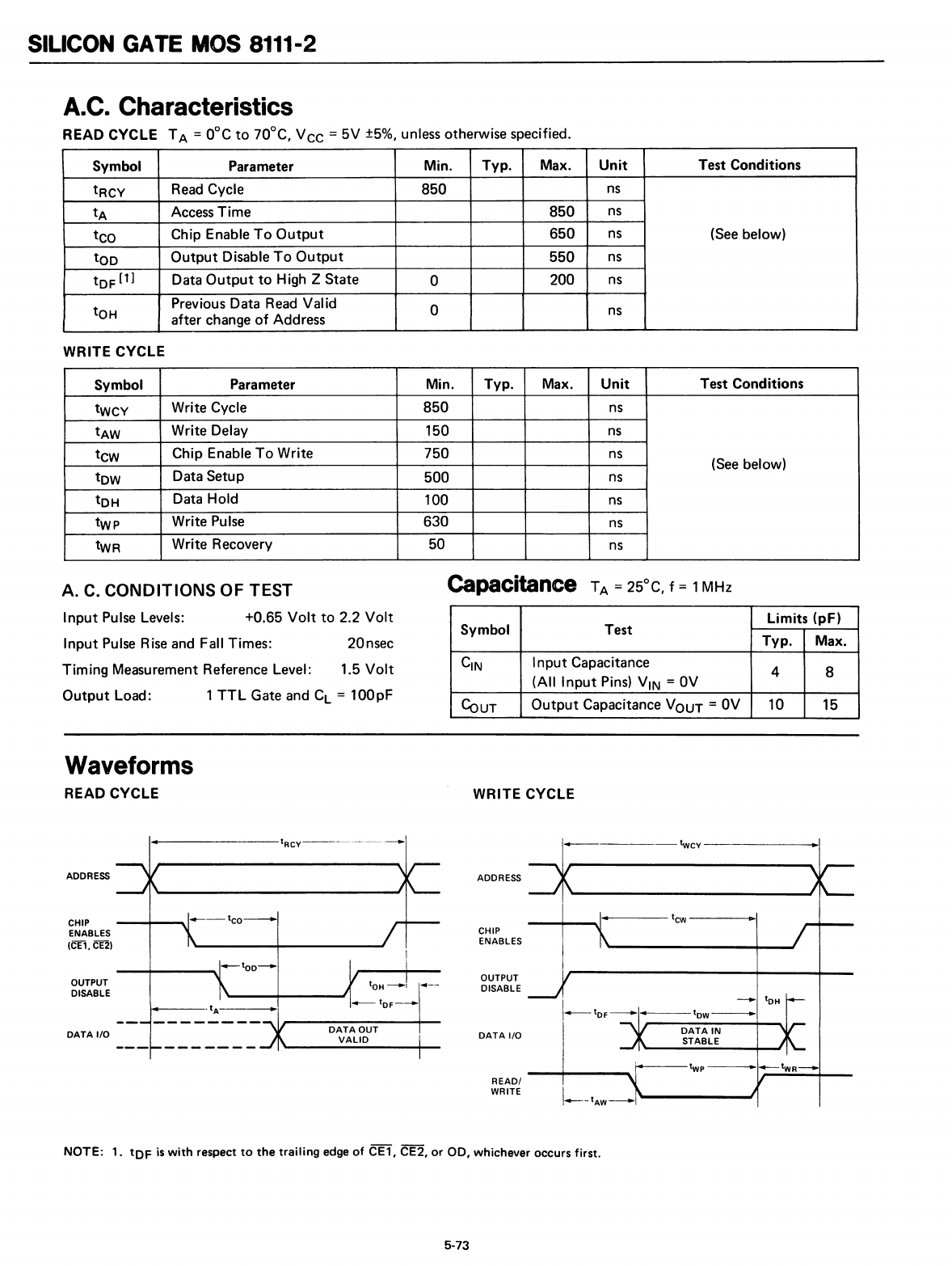

A.C. Characteristics

READ CYCLE TA =

o°c

to

70°C,

Vee

=

5V

±5%,

unless otherwise specified.

Symbol

Parameter

Min.

Typ.

Max. Unit

Test

Conditions

tRCY

Read Cycle

850

ns

tA

Access Time

850

ns

tco

Chip Enable To

Output

650

ns

(See below)

too

Output Disable

To

Output

550

ns

tOF

[1]

Data

Output

to

High

Z State

0

200

ns

tOH

Previous Data Read Valid

0

ns

after change of Address

WRITE CYCLE

Symbol Parameter Min.

Typ.

Max. Unit

Test

Conditions

twCY

Write Cycle

850

ns

tAW

Write Delay

150

ns

tcw

Chip Enable To Write

750

ns

(See below)

tow

Data Setup

500

ns

tOH

Data Hold

100

ns

twP

Write Pulse

630

ns

tWR

Write Recovery

50

ns

A.

C.

CONDITIONS OF TEST

Capacitance TA =25°C, f = 1

MHz

Input Pulse

Levels:

+0.65 Volt

to

2.2 Volt

Input Pulse

Rise

and Fall Times: 20nsec

1 TTL Gate and

CL

= 100pF

Timing Measurement Reference Level:

Output Load:

1.5 Volt

Symbol

Test

Limits

(pF)

Typ.

Max.

CIN

Input Capacitance

4

8

(All

Input

Pins)

VIN

=

OV

GoUT

Output Capacitance

VOUT

=

OV

10

15

Waveforms

READ

CYCLE

WRITE CYCLE

DATA

IN

STABLE

----twey------

..I

I

~

tOH

~

t

OF

----.I

....

--t

ow

---.

_

.........

_""I

..

---tew---

..

I

OUTPUT

DISABLE

DATA

I/O

CHIP

ENABLES

ADDRESS

DATA

OUT

VALID

OUTPUT

DISABLE

1..-------tReY-----~

CHIP - .........

-""

1"--

teo

ENABLES

tCE1,

CE2)

ADDRESS

DATA

I/O

1~-tAW--.I""-----"

I

_---+

"'"

f4---lwp

------..............-

tWR~

READ/

WRITE

NOTE:

1.

tOF

is

with respect

to

the

trailing edge

of

eEl,

CE2,

or

00,

whichever occurs first.

5-73