high-order addr

o I 0 I 1 I 1

1

1 1 0 I 1 I 0

low-order addr

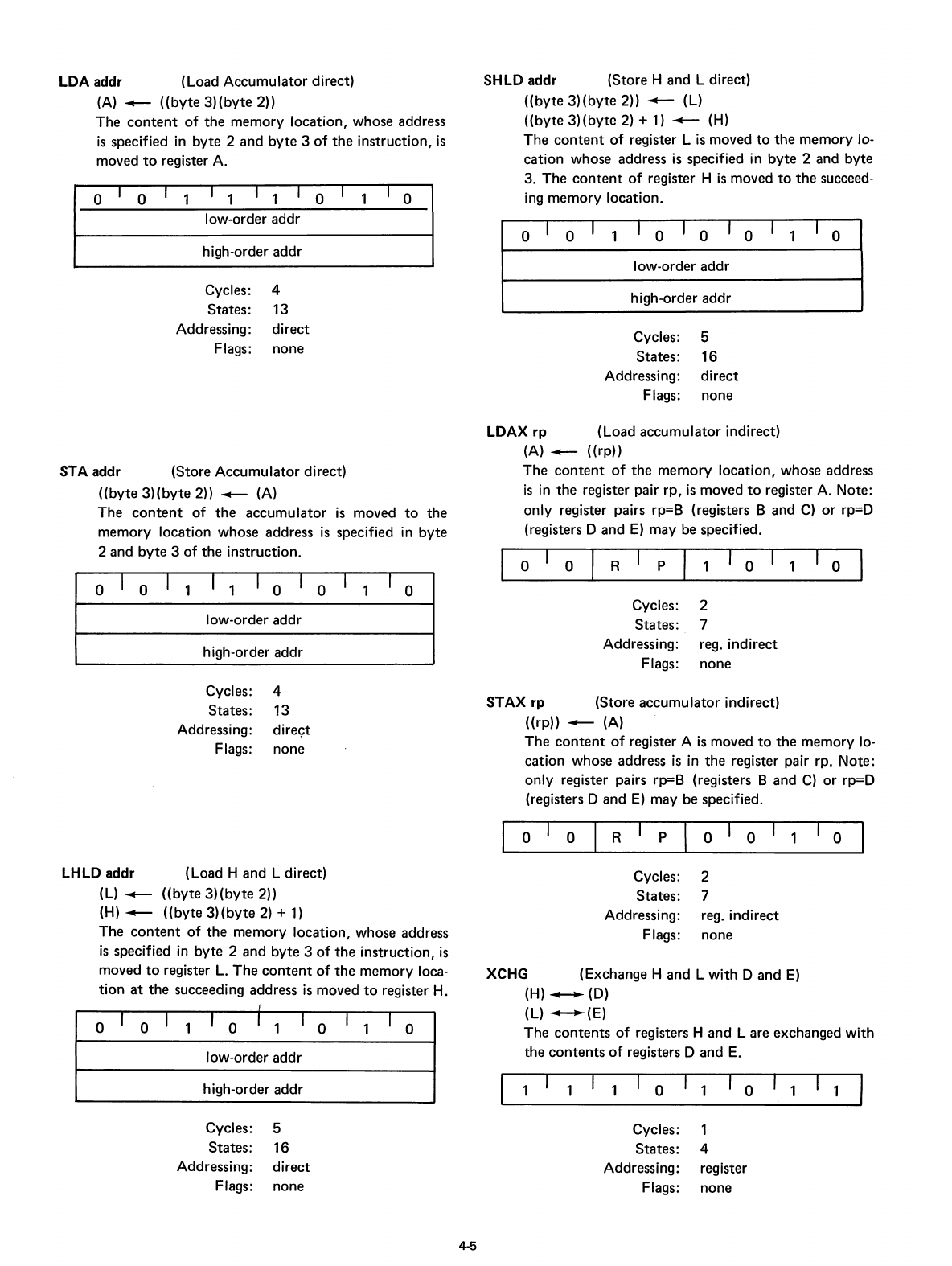

LOA addr (Load Accumulator direct)

(A)

~

((byte 3) (byte

2))

The

content

of

the memory location, whose address

is

specified

in

byte 2 and byte 3

of

the

instruction,

is

moved

to

register

A.

0

I

0

I

1

I 0

I 0

T

0

T

1

I 0

low-order addr

high-order addr

5

16

direct

none

Cycles:

States:

Addressing:

Flags:

SHLD addr (Store

Hand

L direct)

((byte 3) (byte

2))

~

(L)

((byte

3)(byte

2) + 1)

~

(H)

The

content

of

register L

is

moved

to

the

memory

Jo-

cation whose address

is

specified

in

byte 2 and byte

3. The

content

of

register H

is

moved

to

the

succeed-

ing

memory location.

4

13

direct

none

Cycles:

States:

Addressing:

Flags:

LOAX rp (Load accumulator indirect)

(A)~

((rp))

The

content

of

the

memory location, whose address

is

in

the

register pair rp,

is

moved

to

register

A.

Note:

only register pairs rp=B (registers B and

C·)

or

rp=D

(registers D and

E)

may be specified.

Cycles:

States:

Addressing:

Flags:

STA addr (Store Accumulator direct)

((byte

3)(byte

2))

~

(A)

The

content

of

the

accumulator

is

moved

to

the

memory location whose address

is

specified

in

byte

2 and byte 3

of

the instruction.

0

I

0

I

1

I 1

I 0

I

0

I

1

r 0

low-order addr

high-order addr

o I 0 I R

p

2

7

reg. indirect

none

Cycles:

States:

Addressing:

Flags:

4

13

dire<;t

none

STAX rp (Store accumulator indirect)

((rp))

~

(A)

The

content

of

register A

is

moved

to

the

memory

lo-

cation whose address

is

in

the

register pair rp. Note:

only register pairs rp=B (registers B and

C)

or

rp=D

(registers D and

E)

may be specified.

o I 0 I R

XCHG

(Exchange

Hand

L with D and

E)

(H)~(D)

(L)~(E)

The

contents

of

registers

Hand

L are exchanged with

the

contents

of

registers D and

E.

LHLD addr (Load

Hand

L direct)

(L)

~

((byte

3)(byte

2))

(H)

~

((byte 3) (byte 2) + 1)

The

content

of

the memory location, whose address

is

specified

in

byte 2 and byte 3

of

the

instruction,

is

moved

to

register

L.

The

content

of

the

memory loca-

tion

at

the

succeeding address

is

moved

to

register

H.

f

0

I

0

I

1

I

0

I

1

I

0

I

1

T 0

low-order addr

high-order addr

Cycles:

States:

Addressing:

Flags:

I 1 I 0

2

7

reg. indirect

none

Cycles:

States:

Addressing:

Flags:

5

16

direct

none

Cycles:

States:

Addressing:

Flags:

1

4

register

none

4-5