SCHOTTKY BIPOLAR

8205

APPLICATIONS OF THE 8205

The

8205 can be used

in

a wide variety

of

applications

in

microcomputer systems. I/O ports can be decoded from

the

address bus, chip select signals can be generated

to

select

memory devices and

the

type

of

machine

state

such as

in

8008 systems can be derived from a simple decoding

of

the

state lines

(SO,

S1, S2)

of

the

8008

CPU.

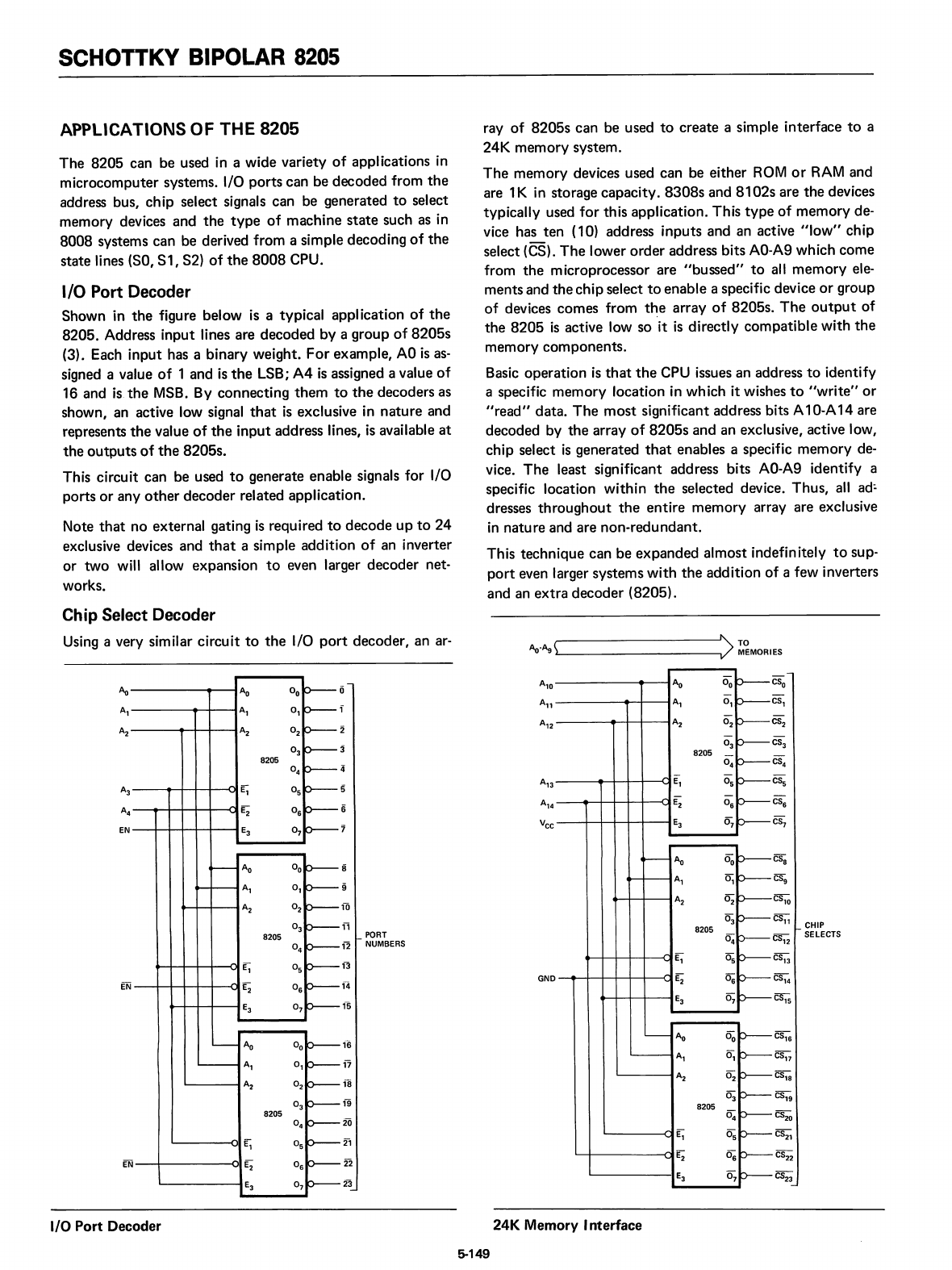

I/O Port Decoder

Shown in

the

figure below

is

a typical application

of

the

8205. Address input lines are decoded by a group

of

8205s

(3). Each input has a binary weight.

For

example,

AO

is

as-

signed a value

of

1 and

is

the

LSB;

A4

is

assigned a value

of

16 and

is

the

MSB.

By connecting

them

to

the

decoders as

shown, an active low signal

that

is

exclusive in nature and

represents

the

value

of

the

input address lines,

is

available

at

the

outputs

of

the

8205s.

This circuit can be used

to

generate enable signals for I/O

ports

or

any

other

decoder related application.

Note

that

no external gating

is

required

to

decode

up

to

24

exclusive devices and

that

a simple addition

of

an inverter

or

two will allow expansion

to

even larger decoder net-

works.

ray

of

8205s can be used

to

create a simple interface

to

a

24K memory system.

The

memory devices used can be either

ROM

or

RAM

and

are 1K in storage capacity.

8308s

and

8102s

are

the

devices

typically used

for

this application. This

type

of

memory de-

vice has

ten

(1

0)

address inputs and an active

"low"

chip

select (CS).

The

lower order address bits

AO-A9

which come

from

the

microprocessor are

"bussed"

to

all memory ele-

ments and

the

chip select

to

enable a specific device

or

group

of

devices comes from

t~e

array

of

8205s.

The

output

of

the

8205

is

active low so it

is

directly compatible with

the

memory components.

Basic operation

is

that

the

CPU issues an address

to

identify

a specific memory location in which it wishes

to

"write"

or

"read"

data.

The

most

significant address bits A1

O-A

14 are

decoded by

the

array

of

8205s and an exclusive, active low,

chip select

is

generated

that

enables a specific memory de-

vice.

The

least significant address bits

AO-A9

identify a

specific location within

the

selected device. Thus,

all

ad:

dresses

throughout

the

entire memory array are exclusive

in

nature and are non-redundant.

This technique can be expanded almost indefinitely

to

sup-

port

even larger systems with

the

addition

of

a few inverters

and an extra decoder (8205).

:>

~~MORIES

A

o

~

A,

0,

CS,

A

2

CS

2

CS

3

8205

CS

4

~

CSs

E;

CS

6

E

3

CS;

Ao

cs;

A,

csg

A

2

CS,o

CS

ll

CHIP

8205

CS'2

SELECTS

~

CS

t3

e;

CS'4

E

3

~

Ao

CS'6

A,

~

CS

17

A

2

CS'8

CS'9

8205

CS

20

e;

CS

2

,

e;

CS

22

E

3

CS

23

A,O----~......-.-I

A

ll

----.-..-t--I

A'2

---""-'+--+---4

24K Memory Interface

Ao-Ag''-

_

fo

fi

PORT

1"2

NUMBERS

13

14

GND

15

i6

17

is

f9

20

21

22

23

Chip Select Decoder

Using a very similar circuit

to

the

I/O

port

decoder, an

ar-

Ao

A

o

°0

A,

A,

0,

A

2

A

2

°2

°3

8205

°4

A

3

E;

Os

A

4

E2

EN

E

3

A

o

°0

A,

0,

A

2

°2

°3

8205

°4

E;

°5

EN

~

°6

E

3

Ao

A,

0,

A

2

°2

°3

8205

°4

~

°5

EN

E2

°6

E

3

°7

I/O Port Decoder

5-149