SILICON GATE MOS M8080A

ABSOLUTE MAXIMUM RATINGS*

Temperature

Under

Bias

-55°C

to

+125°C

Storage Temperatu

re

..

. . . . . . . . . . . . . _65°C

to

+

150°

C

All

Input

or

Output

Voltages

With

Respect

to

VBB

-0.3V

to

+20V

Vcc,

Voo

and Vss

With

Respect

to

VBB

-0.3V

to

+20V

Power Dissipation . . . . . . . . . . .

..

1.7W

*COMMENT: Stresses above those listedunder "Absolute Maxi-

mum

Ratings"

may

cause

permanent damage to the device.

This

is

a stress rating

only

and

functional

operation

of

the

de-

vice

at

these

or

any

other

conditions above those indicated in

the operational sections

of

this specification

is

not

implied. Ex-

posure

to absolute

maximum

rating conditions

for

extended

periods

may

affect

device reliability.

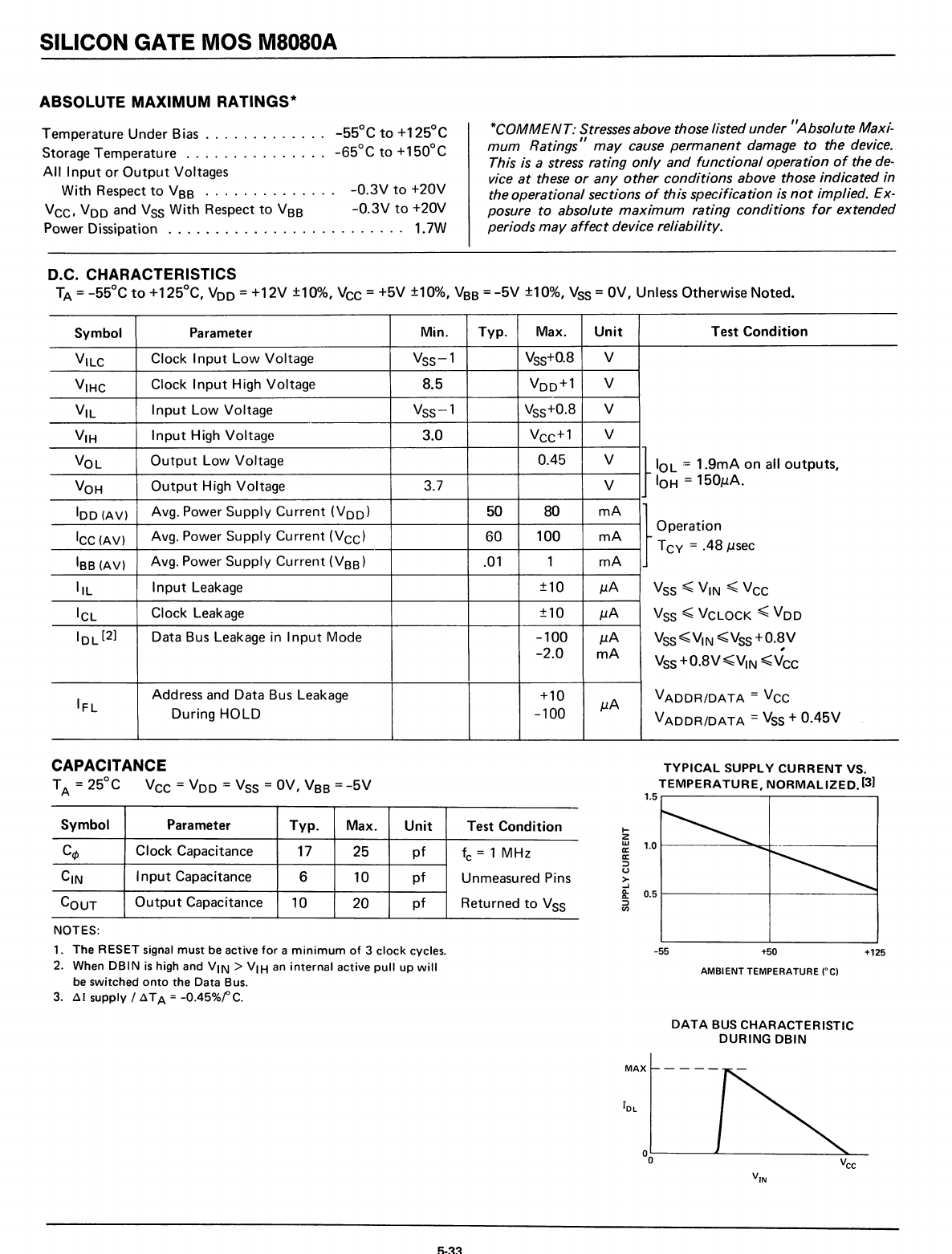

D.C. CHARACTERISTICS

T

A

=

-55°C

to

+125°C,

VOD

=

+12V

±10%, Vee =

+5V

±10%,

VBB

=

-5V

±10%, Vss = OV, Unless

Otherwise

Noted.

Symbol Parameter

Min.

Typ.

Max.

Unit

Test

Condition

VILC

Clock

Input

Low

Voltage

Vss-l

Vss+0.8

V

VIHC

Clock

Input

High Voltage

8.5

Voo+1

V

V

IL

Input

Low

Voltage

Vss-l

V

ss

+0.8

V

V

IH

Input

High Voltage

3.0

Vcc+1

V

VOL

Output

Low

Voltage

0.45 V

}

IOL

= 1.9mA

on

all

outputs,

VO

H

Output

High Voltage

3.7

V

IOH

= 150J-lA.

IOD(AV)

Avg. Power

Supply

Current

(V

oo

)

50

80

rnA

ICC

(AV)

Avg. Power

Supply

Current

(Vec)

60

100

mA

} Operation

T

Cy

=

.48

J.1.sec

IBB(AV)

Avg. Power

Supply

Current

(V

BB

)

.01 1

mA

IlL

I

nput

Leakage

±10

J1A

V

ss

~

VIN

~

V

cc

I

CL

Clock Leakage

±10

J1A

Vss

~

VCLOCK

~

VDD

I

DL

[2]

Data Bus Leakage in I

nput

Mode

-100

J1A

VSS

~VIN

~VSS

+O.~V

-2.0

rnA

VSS

+0.8V

~VIN

~VCC

IFL

Address and Data Bus Leakage

+10

J1A

VADDR/DATA =

VCC

During

HOLD

-100

VADDR/DATA = Vss + O.45V

+125

AMBIENT TEMPERATURE

rc)

+50

-55

TYPICAL

SUPPLY

CURRENT

VS.

TEMPERATURE,

NORMALIZEO.l3]

1.5,.....------r-----------,

I-

2

~

1.0

J---------:::::l~I------______I

a:

:::>

u

>

...J

8:

0.5

t------J-------______I

:::>

en

Symbol

Parameter

Typ.

Max.

Unit

Test

Condition

C¢

Clock

Capacitance

17

25

pf

f

c

= 1

MHz

CIN

I

nput

Capacitance

6

10

pf

Unmeasured Pins

CO

UT

Output

Capacitance

10

20

pf

Returned

to

Vss

NOTES:

1.

The

RESET

signal

must

be

active for a minimum of 3 clock

cycles.

2.

When

DBIN

is

high

and

VIN

>

VIH

an

internal active pull

up

will

be

switched onto

the

Oata

Bus.

3.

~

I supply /

~

TA =

-0.45%/

C.

CAPACITANCE

T

A

=

25°C

Vec

= V

OD

= Vss = OV,

VBB

=-5V

DATA

BUS

CHARACTERISTIC

DURING

DBIN

MAX

°0"----------------------30--

Vee