SILICON GATE MOS 8080A

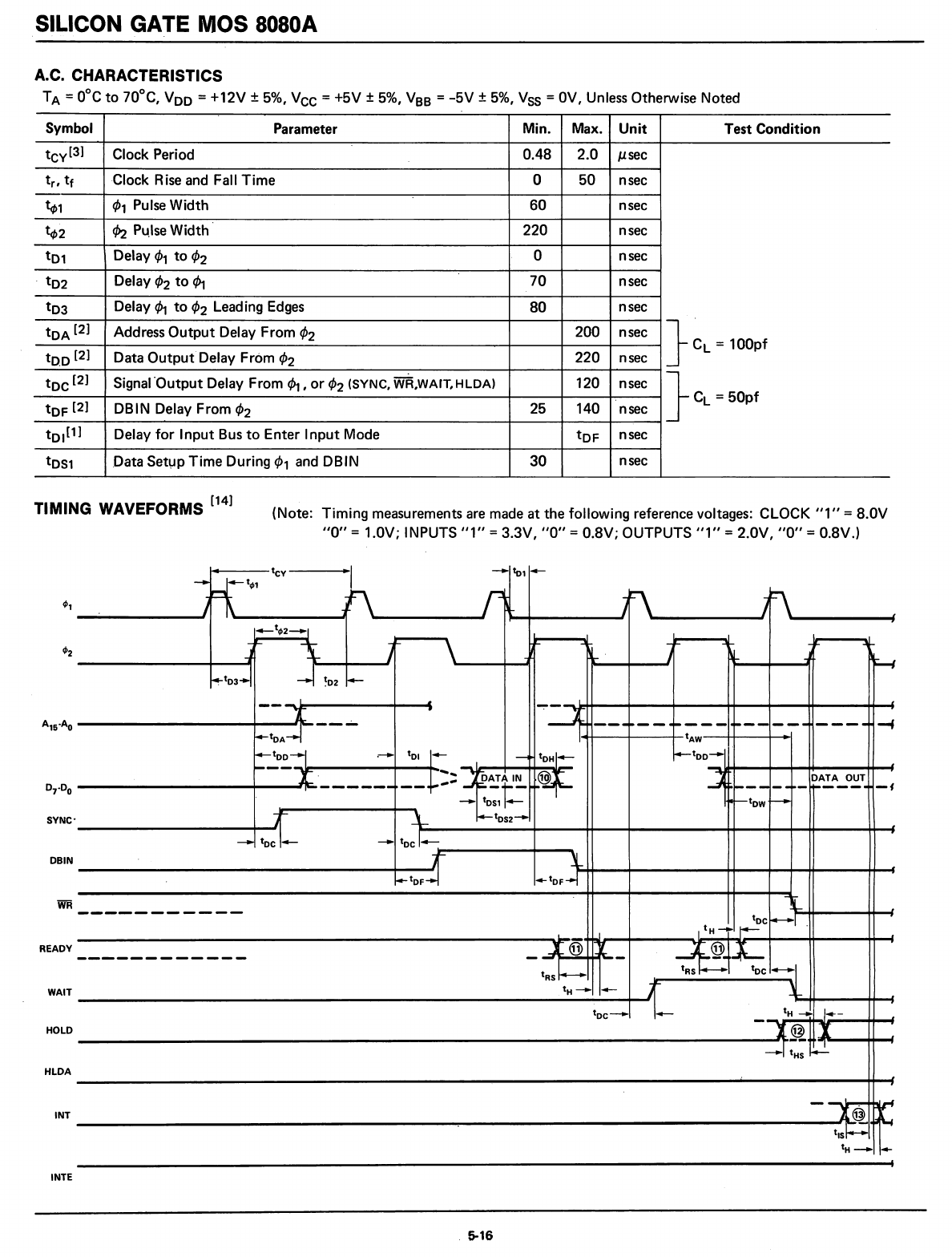

A.C. CHARACTERISTICS

T

A

=

O°C

to

70°C,

VOO

=

+12V

± 5%,

VCC

=

+5V

±

5%,

Vas =

-5V

±

5%,

Vss =

OV,

Unless Otherwise Noted

Symbol

Parameter

Min. Max.

Unit

Test

Condition

tCy[3]

Clock Period 0.48 2.0

J1sec

t

r

,

tf

·Clock Rise and Fall

Time

0 50

nsec

~1

f/J1

Pulse

Width

60

nsec

tq,2

cf>2

Pu.lse

Width

220 nsec

t01

Delayep1

to

ep2

0 nsec

.

t02

Delay

lP2

to

l/>,

70 nsec

t03

Delayep,

to

ep2

Leading

Edges

80

nsec

tOA [2]

Address

Output

Delay From

~2

200 nsec

}

Cl

= 100pf

to.D

[2]

Data

Output

Delay From

f/J2

220

nsec

toC[2]

Signal

'Output

Delay From

ep1

,

or

ep2

(SYNC,

WR,WArT,

HLDA) 120 nsec

}Cl

=50pf

tOF

[2]

DBIN

Delay From

lP2

25 140

nsec

tOI[1]

Delay

for

Input

Bus

to

Enter

Input

Mode

tOF

nsec

tOS1

.Data

Set~p

Time

During

~1

and DBIN

30

nsec

TIMING WAVEFORMS [14]

(Note:

Timing

measurements

are

made at the

following

reference voltages: CLOCK

"1"

=

8.0V

"0"

= 1.0V; INPUTS

"1"

=3.3V,

110"

=

0.8V;

OUTPUTS

"1"

=

2.0V,

"0"

=0.8V.)

(/>,

SYNC·

DBIN

READY

WAIT

HOLD

HLDA

INT

INTE

t

CY

-I

-.

to,

.-

--.

~~1

I

f\

r~

JF\

iF\

.-t<l>2~1

j~

}~

~

~

jJ-

....

h

...

F-

~~

~

~~

H

~to3

..

1

!O2

~

___

I

.

~

r.

.

~tOA-.I

--..;..

---

--

----

~--

---

----

-f

tAW

~too--'

~

t

OI

I.........

---i

toHI"'-

...-t

OO

-'

~

r·

4=

.....

-"r-

DATA

IN

~

.J

DATA

OUT

,,"".J--

t

1---

--

-

----

-I

,-------

--

~--

--.

tos,

...-

~I--tow

r---.

T

-t-

~tOS2-'

~

tocl~

---..

t

oc

1..-

-r

1-

~tOF~

~tOF

-----------

~t

t

oc

.........1 .

ItHl~

------------

-I=@

t

-

-;f!1~

-~:'J>

t

RS

t

oc

..........1

t

H

-.

.--

X-

l-

t

oc

---"

1.-

t

H

-.

1.--

--

J@

I

~I~;~~

--X@

,.

tiS

1=-=

~~

t

H

--.

~

. 5-16