SILICON GATE MOS

8251

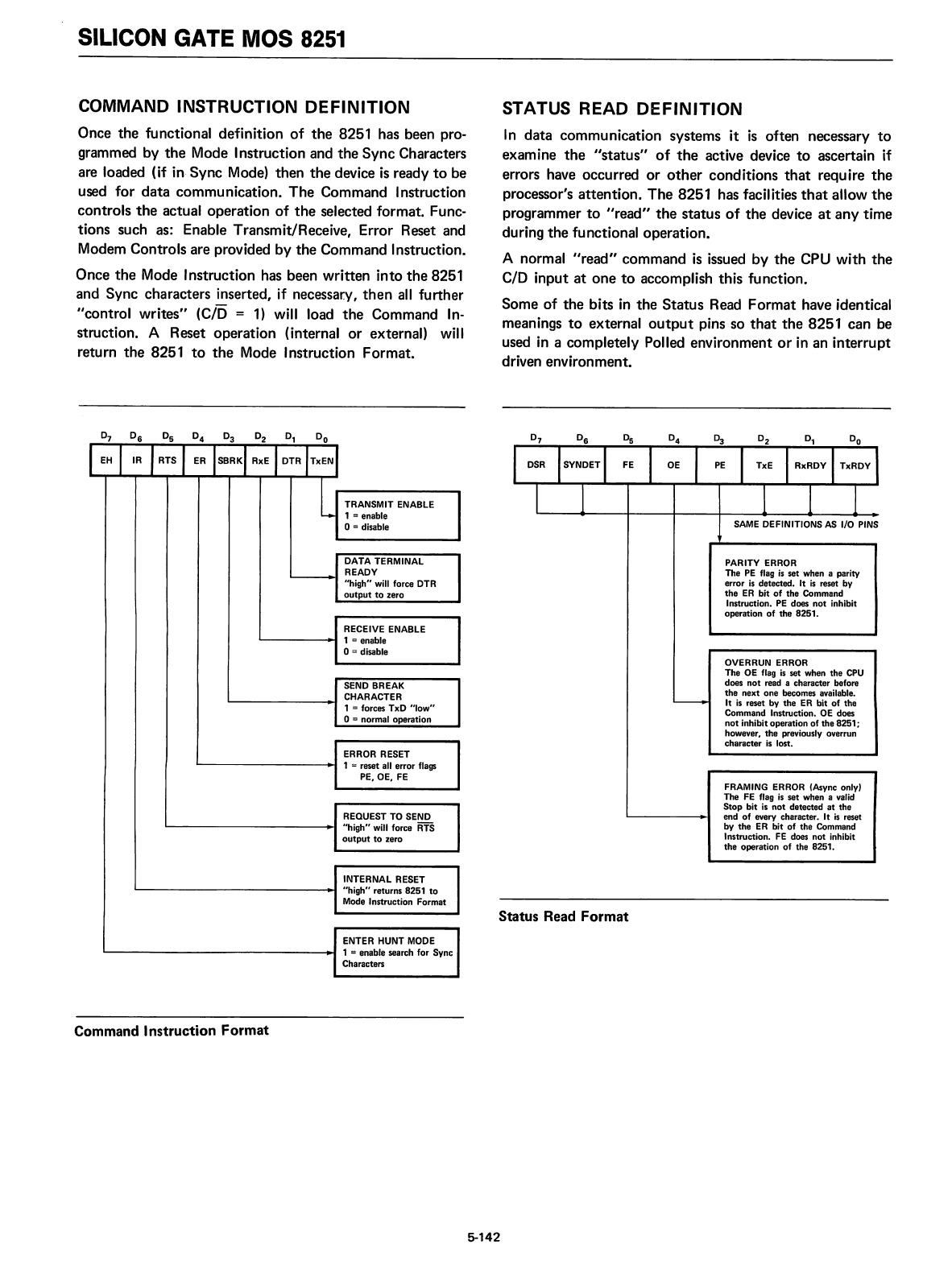

COMMAND INSTRUCTION DEFINITION

Once

the

functional definition

of

the

8251 has been pro-

grammed by

the

Mode Instruction and

the

Sync

Characters

are loaded (if

in·

Sync

Mode)

then

the

device

is

ready

to

be

used for

data

communication.

The

Command Instruction

controls

the

actual operation

of

the

selected format. Func-

tions such as: Enable Transmit/Receive, Error Reset and

Modem Controls are provided by

the

Command Instruction.

Once

the

Mode Instruction has been written

into

the

8251

and Sync characters inserted, if necessary,

then

all

further

"control

writes"

(C/O =

1)

will load

the

Command

In-

struction. A Reset operation (internal

or

external) will

return

the

8251

to

the

Mode Instruction Format.

STATUS READ DEFINITION

In

data

communication systems it

is

often necessary

to

examine

the

"status"

of

the

active device

to

ascertain if

errors have occurred

or

other

cond

itions

that

require

the

processor's attention.

The

8251 has facilities

that

allow

the

programmer

to

"read"

the

status

of

the

device

at

any

time

during

the

fu nctional operation.

A normal

"read"

command

is

issued

by

the

CPU with

the

C/O input

at

one

to

accomplish this function.

Some

of

the

bits

in

the

Status

Read

Format

have identical

meanings

to

external

output

pins so

that

the

8251

can

be

used

in

a completely Polled environment

or

in

an

interrupt

driven environment.

TRANSMIT ENABLE

1 = enable

0=

disable

SAME DEFINITIONS

AS

I/O PINS

DATA TERMINAL

~

READY

"high"

will

force DTR

output

to

zero

RECEIVE ENABLE

'------~

1 = enable

0=

disable

SEND BREAK

CHARACTER

1

=forces TxD

"Iow"

o=normal operation

ERROR RESET

-----------..

1 =reset all error flags

PE, OE, FE

REQUEST TO SEND

L.--

--..

"high"

will force RTS

output

to

zero

INTERNAL RESET

L.--

.......

"high"

returns 8251

to

Mode Instruction Format

ENTER HUNT MODE

L.--

--..

1 = enable search for Sync

Characters

Command Instruction

Format

PARITY ERROR

The

PE

flag

is

set when a parity

error

is

detected. It

is

reset by

the

ER

bit

of

the

Command

Instruction.

PE

does

not

inhibit

operation

of

the 8251.

OVERRUN ERROR

The OE flag

is

set when

the

CPU

does

not

read a character before

the

next one becomes available.

It

is

reset by the

ER

bit

of

the

Command Instruction. OE does

not

inhibitoperation

of

the

8251;

however,

the

previously overrun

character

is

lost.

FRAMING ERROR (Async only)

The FE flag

is

set when a valid

Stop

bit

is

not

detected

at

the

end

of

every character. It

is

reset

by

the

ER

bit of the Command

Instruction.

FE

does not inhibit

the

operation of the 8251.

Status Read

Format

5-142