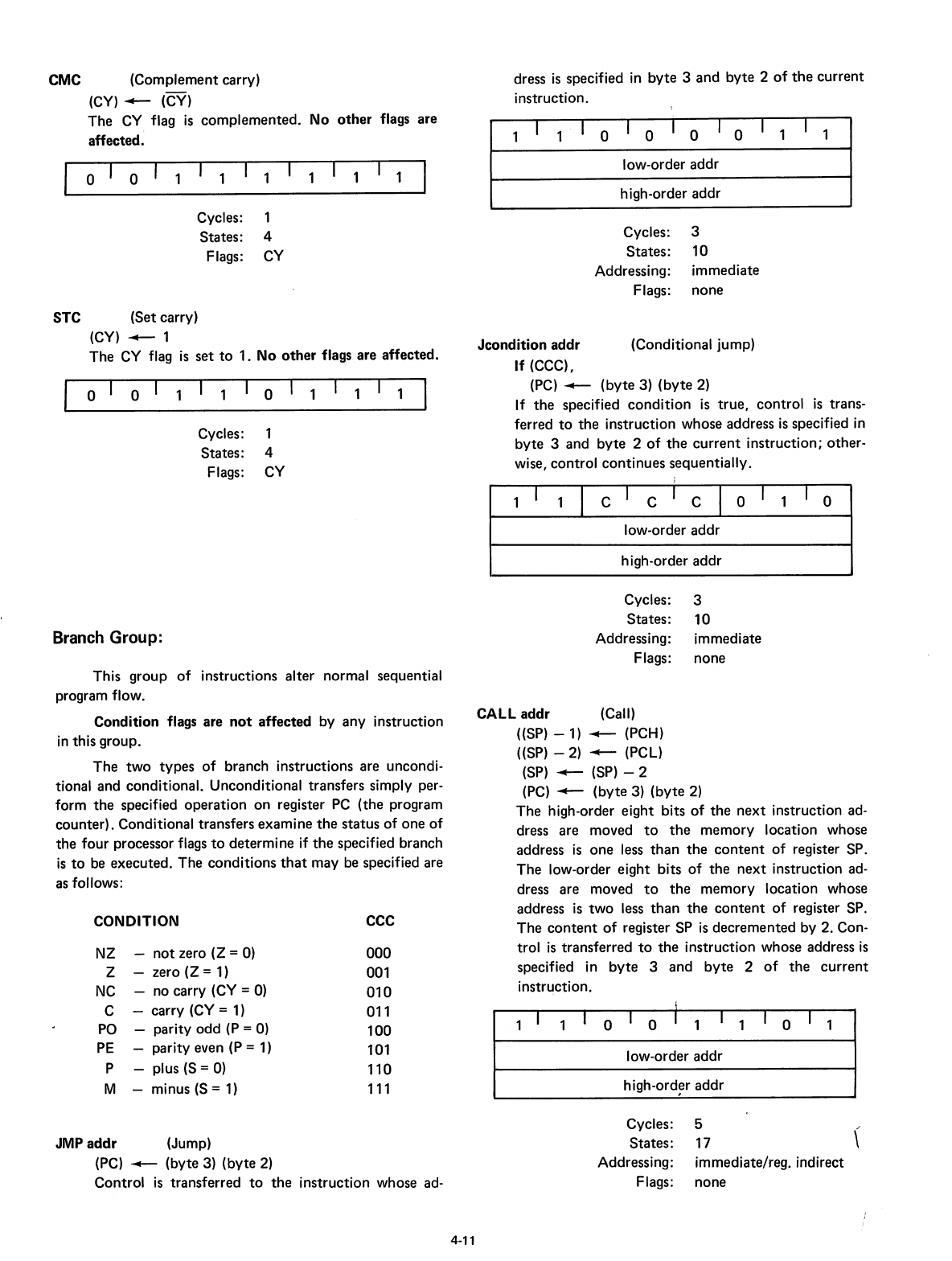

CMC

(Complement

carry)

(CY)~

(CY)

The

CY flag

is

complemented.

No

other

flags

are

affected.

dress

is

specified in

byte

3

and

byte

2

of

the

current

instruction.

I

1

I

0

I

0

I

0

I

0

I

1

I

1

1

low-order

addr

high-order

addr

a , 0 ,

Cycles:

States:

Flags:

1

4

CY

Cycles:

States:

Addressing:

Flags:

3

10

immediate

none

STC

(Set

carry)

(CY)

~

1

The

CY flag

is

set

to

1.

No

other

flags

are

affected.

0

I

0

I

0

I

1

I

1

Cycles:

1

States:

4

Flags: CY

Jcondition

addr

(Conditional

jump)

If

(CCC),

(PC)

~

(byte

3)

(byte

2)

If

the

specified

condition

is

true,

control

is

trans-

ferred

to

the

instruction

whose

address

is

specified in

byte

3

and

byte

2

of

the

current

instruction;

other-

wise,

control

continues

sequentially.

"

1

I

1

I

C

I

C

I

C

I

0

I

1

I

0

low-order

addr

high-order

addr

Branch Group:

This

group

of

instructions

alter

normal

sequential

program flow.

Condition

flags

are

not

affected

by

any

instruction

in

this

group.

The

two

types

of

branch

instructions

are

uncondi-

tional

and

conditional.

Unconditional

transfers

simply per-

form

the

specified

operation

on

register PC

(the

program

counter).

Conditional

transfers

examine

the

status

of

one

of

the

four

processor flags

to

determi

ne if

the

specified

branch

is

to

be

executed.

The

conditions

that

may

be specified are

as follows:

~

1

I

1

I

0

I

0

I

1

T

1

I

0

I

1

low-order

addr

high-ord~r

addr

CALL

addr

(Call)

((SP) -

1)

~

(PCH)

((SP) -

2)

~

(PCl)

(SP)

~

(SP) - 2

(PC)

~

(byte

3)

(byte

2)

The

high-order

eight

bits

of

the

next

instruction

ad-

dress

are

moved

to

the

memory

location

whose

address

is

one

less

than

the

content

of

register SP.

The

low-order

eight

bits

of

the

next

instruction

ad-

dress

are

moved

to

the

memory

location

whose

address

is

two

less

than

the

content

of

register SP.

The

content

of

register SP

is

decremented

by

2. Con-

trol

is

transferred

to

the

instruction

whose

address

is

specified in

byte

3

and

byte

2

of

the

current

instruction.

3

10

immediate

none

Cycles:

States:

Addressing:

Flags:

CCC

000

001

010

011

100

101

110

111

NZ

-

not

zero

(Z

= 0)

2 - zero

(2

= 1)

NC

- no

carry

(CY = 0)

C -

carry

(CY =

1)

PO -

parity

odd

(P = 0)

PE -

parity

even (P =

1)

P - plus (S = 0)

M

-minus(S=1)

CONDITION

JMP

addr

(Jump)

(PC)

~

(byte

3)

(byte

2)

Control

is

transferred

to

the

instruction

whose

ad-

Cycles:

States:

Addressing:

Flags:

5

17

immediate/reg.

indirect

none

4-11