SILICON GATE MOS 8080A-2

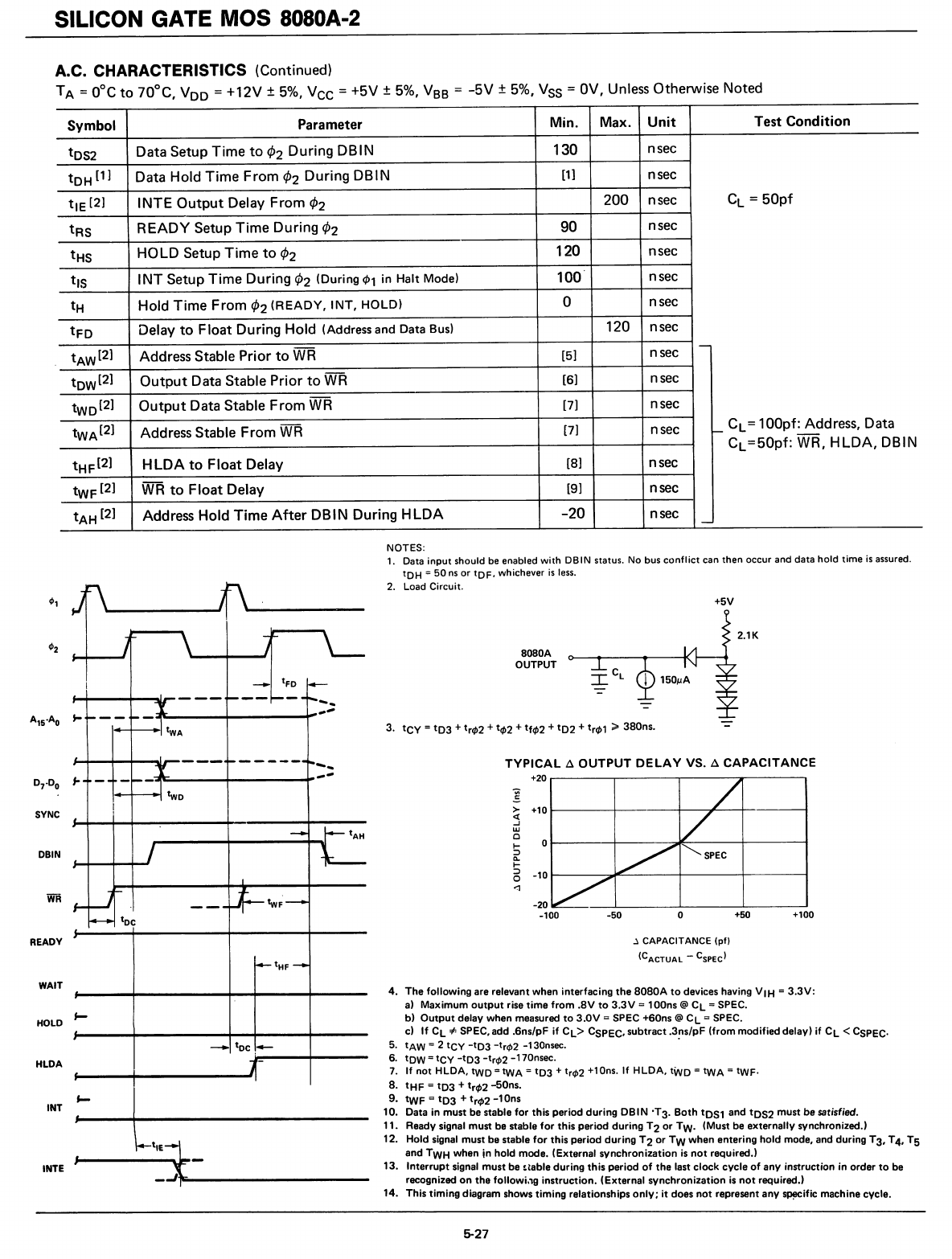

A.C. CHARACTERISTICS (Continued)

TA =

O°C

to

70°C,

VOD

=

+12V

±

5%,

Vee =

+5V

±

5%,

V

BB

=

-5V

±

5%,

V

ss

=

OV,

Unless Otherwise Noted

Symbol

Parameter

Min. Max. Unit

Test

Condition

tOS2

Data Setup

Time

to

<P2

During

DBIN

130

nsec

toH

[1]

Data Hold

Time

From

</>2

During

DBIN

[1]

nsec

tiE

[2]

INTE

Output

Delay From

<P2

200 nsec

CL

=

50pf

tRS

READY

Setup

Time

During

<P2

90

nsec

tHS

HOLD

Setup

Time

to

ep2

120 nsec

tiS

I

NT

Setup

Time

During

cfJ2

(During

<1>1

in

Halt

Mode)

100

nsec

tH

Hold

Time

From

ep2

(READY,

INT,

HOLD)

0 nsec

tFD

Delay

to

Float During

Hold

(Address

and

Data

Bus)

120

nsec

tAW

[2]

Address Stable Prior

to

WR

-

[5]

nsec

tow

[2]

Output

Data Stable

Prior

to

WR

[6]

nsec

tWD[2]

Output

Data Stable

From

WR [7]

nsec

tWA

[2]

Address Stable

From

WR

[7]

nsec

CL= 100pf: Address, Data

-

--

CL

=50pf:

WR,

HLDA,

DBIN

tHF[2]

HLDA

to

Float

Delay

[8]

nsec

tWF[2]

WR

to

Float

Delay

[9]

nsec

tAH[2]

Address Hold

Time

After

DBIN

During

HLDA

-20

nsec

-

+5V

TYPICAL

~

OUTPUT

DELAY

VS.

~

CAPACITANCE

+20,....----.....-------,------y------.

+100

2.1K

+50

~

CAPACITANCE

(pf)

(CACTUAL - C

SPEC

)

o

-50

.=.

> +10

«

-J

w

0

t-

O

:::>

Q..

t-

:::>

-10

0

<1

3.

tCY

=

t03

+t

r

4>2

+

t4>2

+

tf4>2

+

t02

+t

r

4>1

~

380ns.

8080A

OUTPUT

NOTES:

1. Data

input

should

be

enabled

with

DBIN status. No bus

conflict

can then occur and data hold time

is

assured.

tOH =

50

ns

or

tOF. whichever

is

less.

2.

Load Circuit.

t/),

A'S-A

O

to-

tWA

0

7

-0

0

,.

-

two

SYNC

DBIN

WR

t

oc

READY

WAIT

HOLD

I-

HLDA

INT

INTE

I

-...

t

oc

.-

4.

The

following

are relevant when interfacing

the

8080A

to

devices having

V,H

=

3.3V:

a)

Maximum

output

rise

time

from

.8V

to

3.3V

= 100ns@

CL

= SPEC.

b)

Output

delay when measured

to

3.0V

= SPEC +60ns @

CL

= SPEC.

c)

If

CL

#:

SPEC, add .6ns/pF

if

CL>

CSPEC, subtract

.3ns/pF

(from

modified

delay)

if

CL

<

CSPEC.

5.

tAW

=2

tCY

-t03

-t

r

</>2

-130nsec. .

6.

tow

=

tCY

-t03

-tr4>2

-170n5ec.

7.

If

not

HLOA,

two =

twA

=

tD3

+t

r

</>2

+10n5.

If

HLDA,

two =

twA

=tWF.

8. tHF

=

t03

+t

r

4>2

-SOns.

9.

twF

=

t03

+t

r

cf)2

-10ns

10. Data

in

must be stable

for

this

period

during

DBIN

°T3.

Both

tOS1 and tOS2 must besatisfied.

11. Ready signal must be stable

for

this

period

during

T2

or

TW. (Must be externally synchronized.)

12.

Hold

signal

must

be stable

for

this

period

during

T2

or

TW

when entering

hold

mode, and

during

T3,

T4,

T5

and TWH when

in

hold

mode. (External

synchronization

is

not

required.)

13.

Interrupt

signal

must

be

uable

during

this

period

of

the

last

clock

cycle

of

any

instruction

in

order

to

be

recognized

on

the followi,1g

instruction.

(External

synchronization

is

not

required.)

14. This

timing

diagram shows

timing

relationships

only;

it

does

not

represent any

s~ific

machine cycle.

5-27