SILICON GATE MOS 8253

8253 PRELIMINARY

FUNCTIONAL DESCRIPTION

GATE 2

GATE 0

ClK

1

CLKO

CLK2

OUT2

OUT 1

GATE 1

COUNTER

#2

READ/

WRITE

lOGIC

DATA

BUS

BUFFER

INTERNALBUS

cs-------'

AD

--___.a

WR

-----+C11

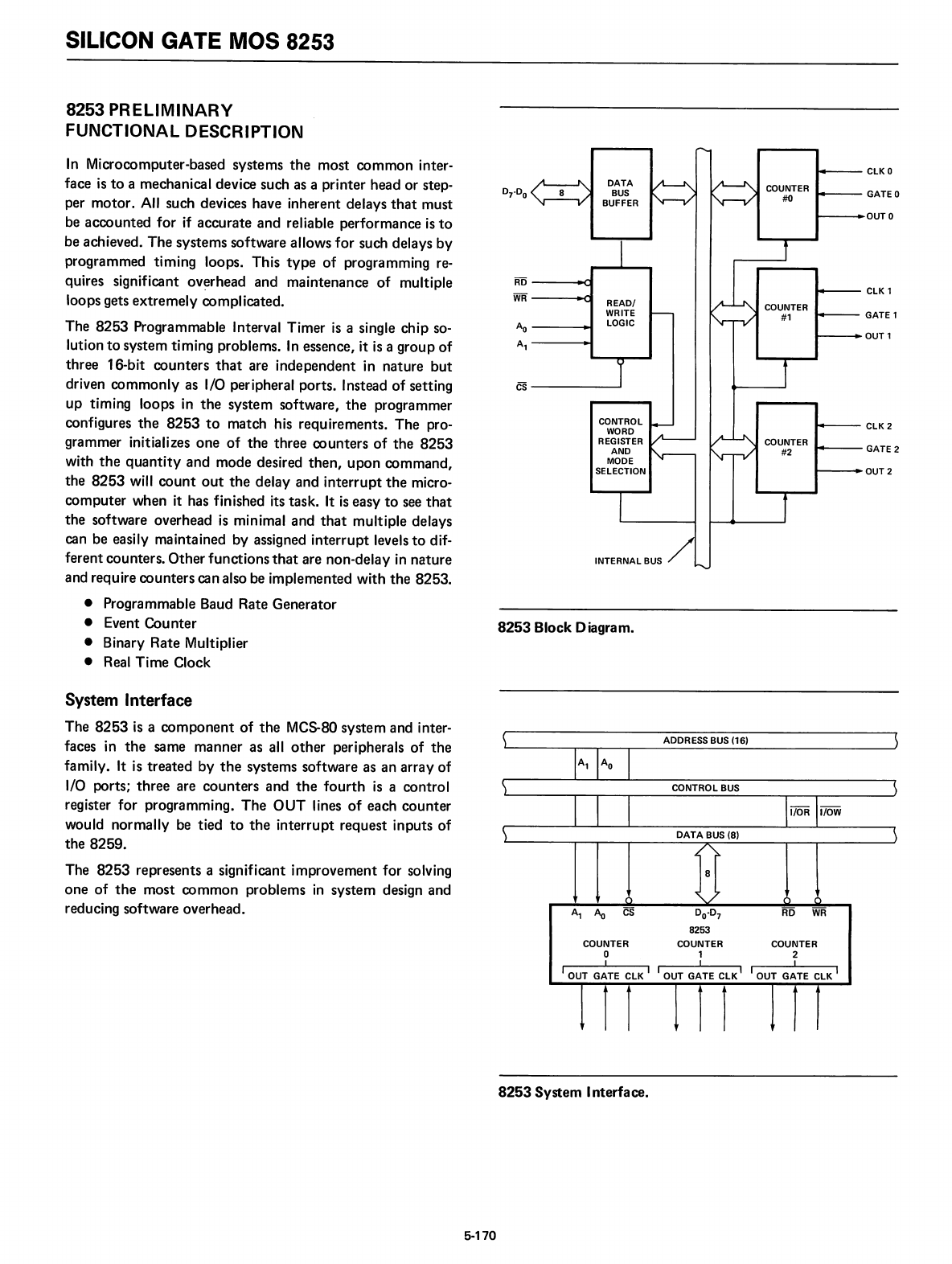

8253 Block Diagram.

In

Microcomputer-based systems

the

most

common

inter-

face

is

to

a mechanical device such as a printer head or step-

per

motor.

All such devices have inherent delays

that

must

be

accounted

for

if accurate

and

reliable performance

is

to

be achieved. The systems software allows

for

such delays

by

programmed timing loops. This

type

of

programming re-

quires significant

ov~rhead

and maintenance

of

multiple

loops gets

extremely

complicated.

The

8253

Programmable Interval Timer

is

a single chip so-

lution

to

system timing problems.

In

essence, it

is

a

group

of

three

16-bit

counters

that

are

independent

in nature

but

driven

commonly

as I/O peripheral ports. Instead

of

setting

up timing loops in

the

system software,

the

programmer

configures

the

8253

to

match his requirements.

The

pro-

grammer initializes

one

of

the

three

counters

of

the

8253

with

the

quantity

and

mode desired

then,

upon

command,

the

8253

will

count

out

the

delay and

interrupt

the

micro-

computer when it has finished its task. It

is

easy

to

see

that

the

software overhead

is

minimal and

that

multiple delays

can be easily maintained by assigned

interrupt

levels

to

dif-

ferent counters. Other

functions

that

are non-delay

in

nature

and require

counters

can also be implemented with

the

8253.

• Programmable Baud Rate Generator

• Event

Counter

• Binary Rate Multiplier

• Real

Time

Clock

System Interface

The

8253

is

a

component

of

the

MC5-80 system and inter-

faces in

the

same manner as all

other

peripherals

of

the

family. It is

treated

by

the

systems software as an array

of

I/O ports;

three

are

counters

and

the

fourth

is

a control

register for programming.

The

OUT

lines

of

each

counter

would normally be tied

to

the

interrupt

request inputs

of

the

8259.

The

8253

represents a significant improvement for solving

one

of

the

most

common

problems

in

system design and

reducing software overhead.

ADDRESS

BUS

(16)

A

1

An

0

0

.0

7

8253

COUNTER COUNTER COUNTER

012

I I I

lOUT

GATE

ClK

I

lOUT

GATE

ClK

I

lOUT

GATE

ClK

I

8253 System Interface.

5

..

170