SILICON GATE MOS 8255

PC, OBF

B

P~.PBo

8

r-

- -,

I INTE I

I A I

__

.J

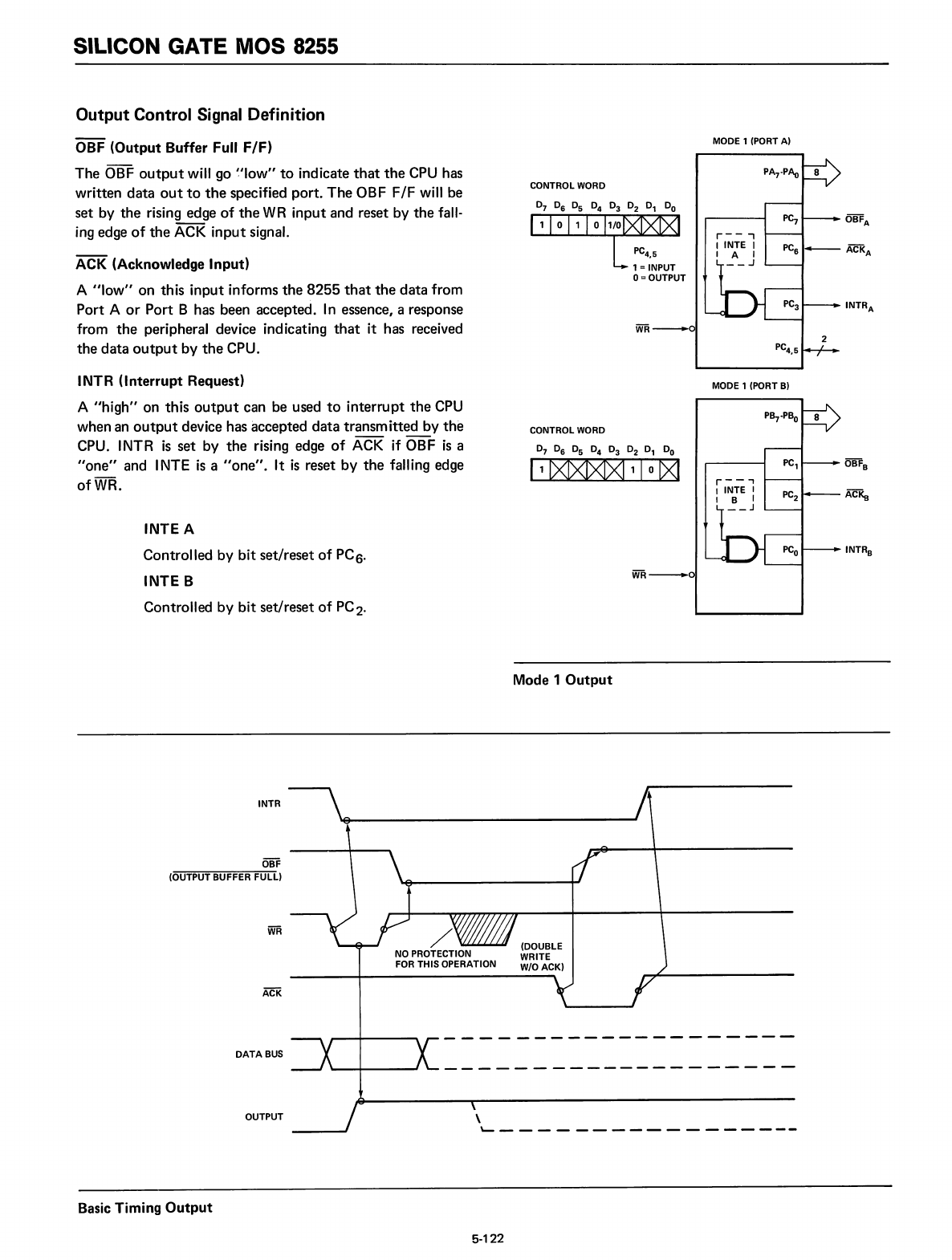

MODE 1 (PORT A)

MODE

1 (PORT B)

CONTROL WORD

CONTROL WORD

0

7

0

6

Os 0

4

0

3

O

2

0,

Do

INTEA

Controlled by bit set/reset

of

PC

6.

INTE

B

Controlled

by

bit

set/reset

of

PC

2.

Output

Control Signal Definition

OBF

(Output

Buffer

Full

F/F)

The OBF

output

will go

~'Iow"

to

indicate

that

the

CPU

has

written data

out

to

the

specified port.

The

OBF F/F will be

set

by

the

rising edge

of

the

WR

input

and reset by

the

fail-

ing edge

of

the

ACK

input

signal.

ACK (Acknowledge Input)

A

"Iow"

on

this

input

informs

the

8255

that

the

data

from

Port A

or

Port B has been accepted.

In

essence, a response

from

the

peripheral device indicating

that

it has received

the

data

output

by

the

CPU.

INTR

(Interrupt Request)

A

"high"

on this

output

can be used

to

interrupt

the

CPU

when an

output

device has accepted

data

transmitted by

the

CPU. INTR

is

set

by

the

rising edge

of

ACK if OBF

is

a

"one"

and INTE

is

a

"one".

It

is

reset

by

the

falling edge

ofWR.

Mode 1

Output

(OUTPUTBUFFER

FULL)

/

NO PROTECTION

FOR THISOPERATION

DATA

BUS

OUTPUT

\

~-

--

-

-----

- -

------

Basic

Timing

Output

5-122