6. The last four lines contain incidental information

about the execution of the instruction. The num-

ber of machine cycles and states required

to

exe-

cute the instruction are listed first.

If

the instruc-

tion has two possible execution times, as

in

a

Conditional Jump·, both times

will

be

listed, sep-

arated by a slash. Next, any significant data ad-

dressing modes'(see

Page

4-2) are listed. The last

line lists any of the five Flags

that

are affected

by

the execution of the instruction.

Data Transfer Group:

This group of instructions transfers data

to

and from

registers and memory. Condition flags are

not

affected

by

any instruction

in

this group.

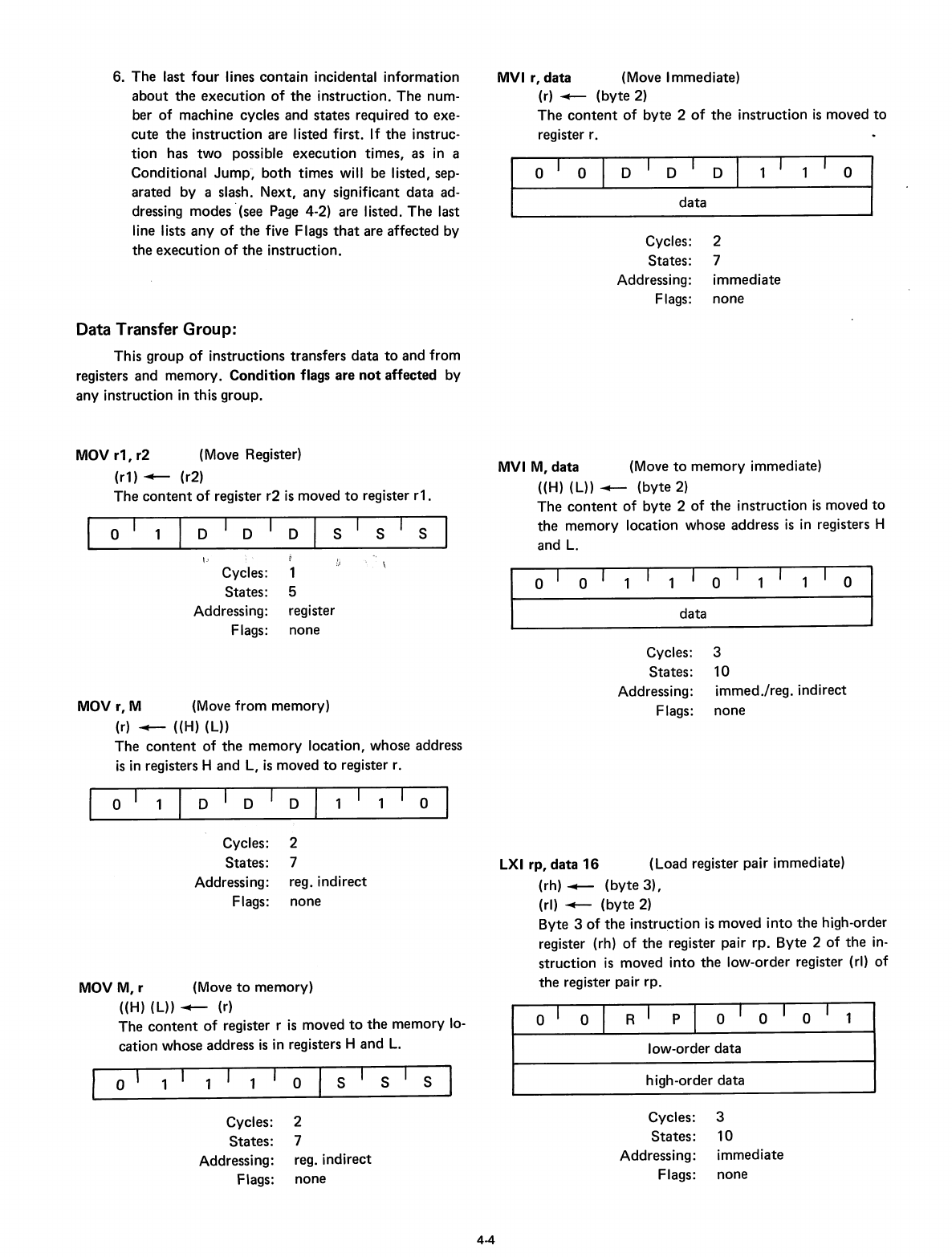

MVI

r, data (Move Immediate)

(r)

~

(byte

2)

The content

of

byte 2

of

the instruction

is

moved to

register

r.

MVI

M,

data

(Move

to

memory immediate)

((H)

(L))

~

(byte

2)

The content of byte 2 of the instruction

is

moved to

the memory location whose address

is

in

registers H

and

L.

MOV

r1, r2

(Move

Register)

(r1)"'-

(r2)

The content of register r2

is

moved

to

register r

1.

0

I

D

I

D

I

D

S

S

I

S

'.1

f'

. \

Cyc·'es:

1

States:

5

Addressing: register

Flags: none

o I 0

data

o

1 ' 1 I 0

MOV

r, M

(Move

from memory)

(r)

~

((H) (L))

The content of the memory location, whose address

is

in

registers

Hand

L,

is

moved

to

register

r.

Cycles:

States:

Addressing:

Flags:

3

10

immed.lreg. indirect

none

1 I

I 0

MOV

M,

r

(Move

to

memory)

((H)(L))~

(r)

The content of register r

is

moved

to

the memory

lo-

cation whose address

is

in

registers

Hand

L.

o ' 1 I

Cycles:

States:

Addressi

ng:

Flags:

2

7

reg. indirect

none

LXI

rp, data

16

(Load register pair immediate)

(rh)

~

(byte 3),

(rl)

~

(byte

2)

Byte 3 of the instruction

is

moved into the high-order

register (rh) of the register pair rp. Byte 2 of the

in-

struction

is

moved into the low-order register

(rl)

of

the register pair rp.

o I

o I

R

1

p I

o I

o I

o I

1

low-order data

high-order data

Cycles:

States:

Addressing:

Flags:

2

7

reg. indirect

none

4-4

Cycles:

States:

Addressing:

Flags:

3

10

immediate

none