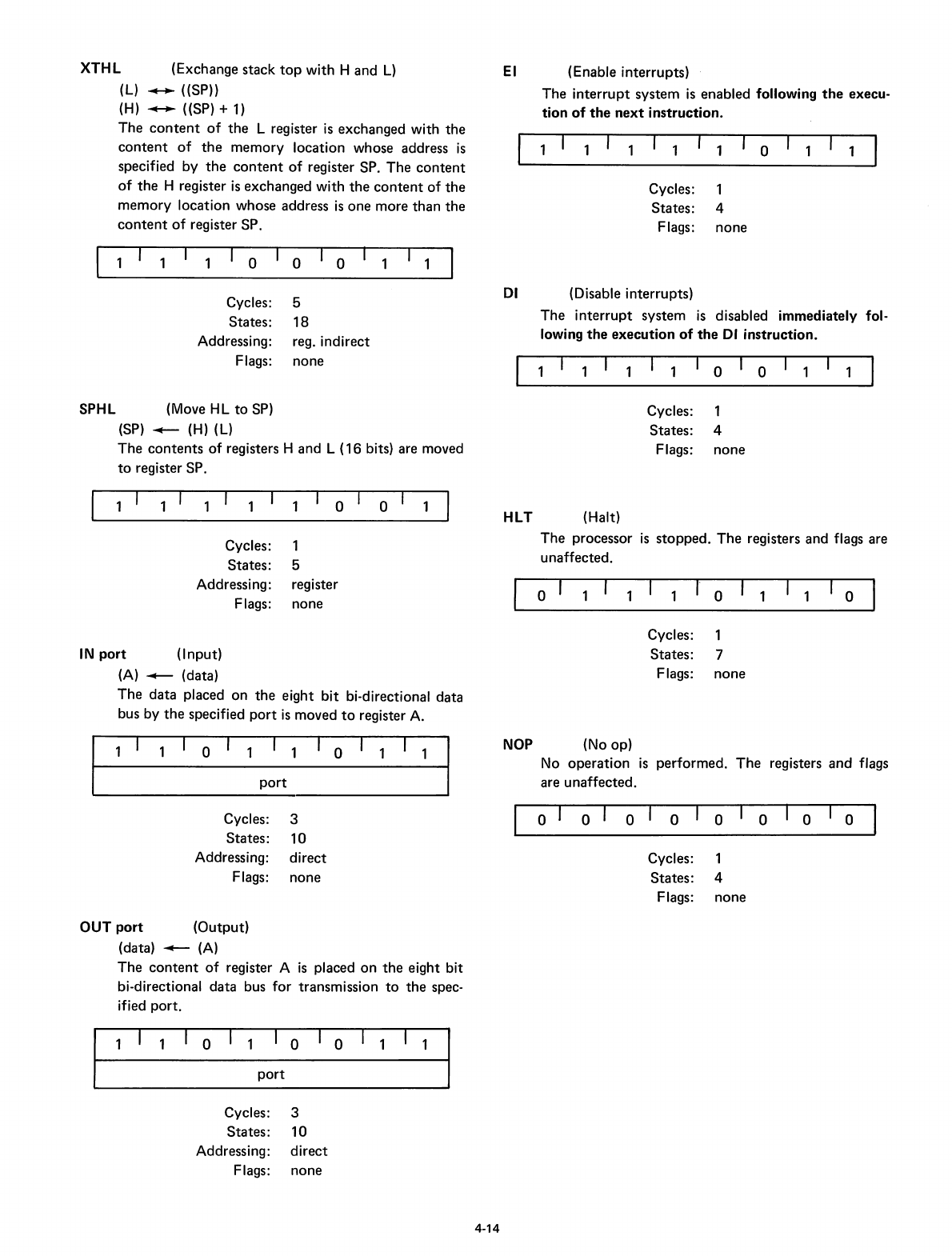

XTHL (Exchange stack

top

with

Hand

L)

(L)

~((SP))

(H)

~

((SP) +

1)

The

content

of

the L register

is

exchanged with the

content

of

the memory location whose address

is

specified by the

content

of register SP. The content

of the

H register

is

exchanged with the content of the

memory location whose address

is

one more than the

content

of register SP.

EI

(Enable interrupts)

The interrupt system

is

enabled following

the

execu-

tion

of

the

next

instruction.

1

I I

1

,

0

I

1

I

1

Cycles:

1

States:

4

Flags:

none

1 I

I 0

o

o

Cycles:

States:

Addressing:

Flags:

5

18

reg.

indirect

none

01

(Disable interrupts)

The interrupt system

is

disabled immediately fol-

lowing

the

execution

of

the

01

instruction.

1

1

0

1

0

'

1

1

1

SPHL

(Move

HL

to

SP)

(SP)

~

(H)

(L)

The contents of registers

Hand

L (16 bits) are moved

to

register SP.

Cycles: 1

States:

4

Flags: none

IN port

(I

nput)

(A)

~

(data)

The data placed on the eight bit bi-directional data

bus by the specified port

is

moved

to

register

A.

1 I 1 I

Cycles:

States:

Addressing:

Flags:

o

1

5

register

none

o

HLT (Halt)

The processor

is

stopped. The registers and flags are

unaffected.

0

I

1

I

0

I

1

I

1

I

0

Cycles:

1

States:

7

Flags:

none

1 I

I 0 I

I 1 I 0 I 1 I 1

port

NOP (No op)

No

operation

is

performed. The registers and flags

are unaffected.

Cycles: 3

States: 10

Addressing: direct

Flags: none

OUT port (Output)

(data)

~

(A)

The content of register A

is

placed on the eight bit

bi-directional data bus for transmission

to

the spec-

ified port.

0

I

0

I

0

0

0 0

0 0

Cycles:

1

States: 4

Flags: none

o

port

o

Cycles: 3

States: 10

Addressing: direct

Flags: none

4-14