SILICON GATE

MOS

M8080A

M8080A

FUNCTIONAL

PIN

DEFINITION

The

following describes

the

function

of

all

of

the

M8080A

I/O

pi

ns. Several

of

the

descriptions

refer

to

internal

tim

ing periods.

A15-AO

(output'

three~state)

ADDRESS BUS;

the

address

bus

provides

the

address

to

memory

(up

to

64K

8-bit

words)

or

denotes

the

I/O device

number

for

up

to

256

input

and

256

output

devices. A

o

is

the

least significant

address bit.

07

-Do

(input/output

three-state)

DATA

BUS;

the

data

bus

provides bi-directional

communication

between

the

CPU,

memory,

and

I/O devices

for

instructions

and

data

transfers. Also,

during

the

first

clock

cycle

of

each

machine

cycle,

the

M8080A

outputs

a

status

word

on

the

data

bus

that

de-

scribes

the

current

machine

cycle. Do

is

the

least significant bit.

SYNC

(output)

SYNCHRONIZING

SIGNAL;

the

SYNC

pin provides a signal

to

indicate

the

beginning

of

each

machine

cycle.

DBIN

(output)

DATA BUS IN;

the

DBIN signal

indicates

to

external

circuits

that

the

data

bus

is

in

the

input

mode.

This

signal

should

be used

to

enable

the

gating

of

data

onto

the

M8080A

data

bus

from

memory

or

I/O.

READY

(input)

READY;

the

READY

signal

indicates

to

the

M8080A

that

valid

memory

or

input

data

is

available

on

the

M8080A

data

bus.

This

signal

is

used

to

synchronize

the

CPU

with

slower

memory

or

I/O

devices. If

after

sending

an address

out

the

M8080A

does

not

re-

ceive a

READY

input,

the

M8080A

will

enter

a WAIT

state

for

as

long as

the

READY

line

is

low.

READY

can

also be

used

to

single

step

the

CPU.

WAIT

(output)

WAIT;

the

WAIT signal

acknowledges

that

the

CPU

is

in a WAIT

state.

WR

(output)

WRITE;

the

WR

signal

is

used

for

memory

WRITE

or

I/O

output

control.

The

data

on

the

data

bus

is

stable

while

the

WR

signal

is

active low

(WR

= 0).

HOLD

(input)

HO LD;

the

HO

LD

signal

requests

the

CPU

to

enter

the

HO

LD

state.

The

HO

LD

state

allows an

external

device

to

gain

control

of

the

M8080A

address

and

data

bus as

soon

as

the

M8080A

has

completed

its use

of

these

buses

for

the

current

machine

cycle. It

is

recognized

under

the

following

conditions:

•

the

CPU

is

in

the

HALT

state.

•

the

CPU

is

in

the

T2

or

TW

state

and

the

READY signal

is

active.

As a

result

of

entering

the

HOLD

state

the

CPU

ADDRESS

BUS

(A

15

-A

o

)

and

DATA

BUS

(0

7

-0

0

) will be in

their

high

impedance

state.

The

CPU

acknowledges

its

state

with

the

HOLD AC-

KNOWLEDGE (HLDA) pin.

HLDA

(output)

HOLD

ACKNOWLEDGE;

the

HLDA signal

appears

in

response

to

the

HOLD signal

and

indicates

that

the

data

and

address bus

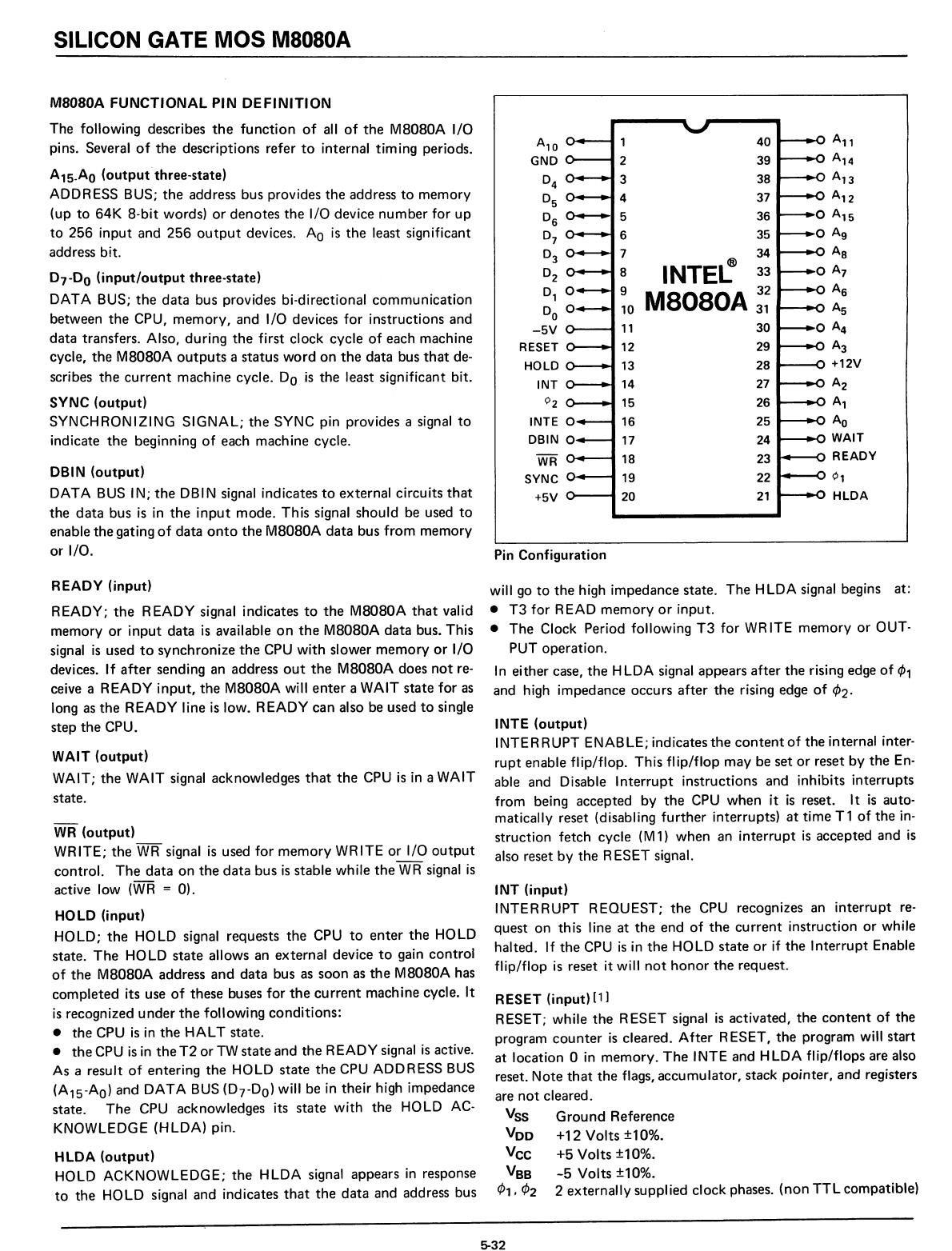

1

40

All

2

39

A

14

3

38

A

13

4

37

A

12

5

36

o A

1S

6

35

o A

g

7

34

As

8

INTE~

33

o A

7

9

M8080A

32

A

6

10

31

As

11

30

o A

4

12

29

A

3

13

28

+12V

14

27

A

2

15

26

A

l

16

25

A

o

17

24

WAIT

WR

18

23

READY

SYNC

19

22

¢l

+5V

20

21

HLDA

Pin

Configuration

will go

to

the

high

impedance

state.

The

HLOA signal begins at:

•

T3

for

READ

memory

or

input.

•

The

Clock Period following

T3

for

WR

ITE

memory

or

OUT-

PUT

operation.

In

either

case,

the

HLOA signal

appears

after

the

rising edge

of

(/)1

and high

impedance

occurs

after

the

rising edge

of

(/)2.

INTE

(output)

INTE RRUPT ENAB LE; indicates

the

content

of

the

internal inter-

rupt

enable

flip/flop.

This

flip/flop

may

be

set

or

reset

by

the

En-

able

and

Disable

Interrupt

instructions

and

inhibits

interrupts

from

being

accepted

by

the

CPU

when

it

is

reset. It

is

auto-

matically reset (disabling

further

interrupts)

at

time

T 1

of

the

in-

struction

fetch

cycle

(M

1)

when

an

interrupt

is

accepted

and

is

also reset

by

the

RESET

signal.

INT

(input)

INTERRUPT

REQUEST;

the

CPU recognizes an

interrupt

re-

quest

on

this

line

at

the

end

of

the

current

instruction

or

while

halted.

If

the

CPU

is

in

the

HOLD

state

or

if

the

Interrupt

Enable

flip/flop

is

reset it will

not

honor

the

request.

RESET

(input)

[1]

RESET; while

the

RESET

signal

is

activated,

the

content

of

the

program

counter

is

cleared.

After

RESET,

the

program will

start

at

location

0 in

memory.

The

INTE

and

HLDA

flip/flops

are also

reset.

Note

that

the

flags,

accumulator,

stack

pointer,

and

registers

are

not

cleared.

Vss

Ground

Reference

Vee

+12

Volts

±10%.

Vee

+5

Volts

±10%.

Vs

s

-5

Volts

±10%.

¢1, ¢2 2

externally

supplied

clock

phases.

(non

TTL

compatible)

5-32