SILICON GATE CMOS

5101,5101-3,

5101L,

5101L-3

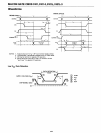

Waveforms

WRITE CYCLE

DATA

IN

STABLE

14-----

t

ew1

---

...

1..-------

t

we

------~

~I-----

t

CW2

------.t

1..----

tDw---~

--.

tAW

104----t

wP

----.I

~

__

-+

__

RIW

CE2

DATA

IN

ADDRESS

00

(COMMON

I/O)

(4)

CE2

DATA

OUT

ADDRESS

READ

CYCLE

..--

_

00

(COMMON I/O) (3]

NOTES: 1. Typical values are for

TA

=25°C

and

nominal supply voltage.

2. This parameter

is

periodically sampled

and

is

not 100% tested.

3.

00

may be tied low for separate I/O

operation.

4. During

the

write

cycle,

00

is

"high"

for

common

I/O and

"don't

care"

for separate I/O

operation.

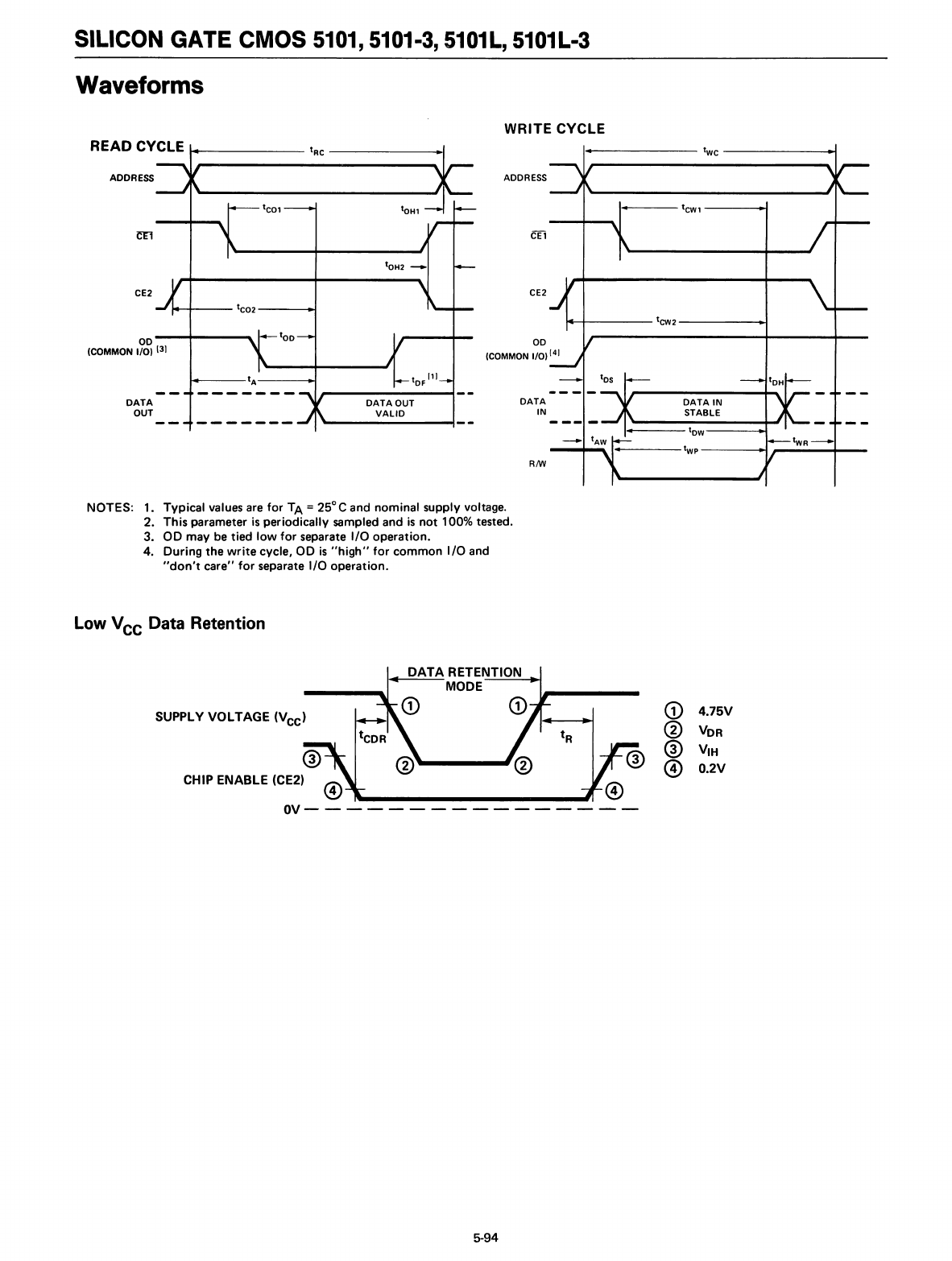

Low

V

CC

Data Retention

DATA

RETENTION

MODE

SUPPLVVOLTAGE (Vee)

®

CHIP

ENABLE

(CE2) @ @

W----------------

<D

4.75V

®

VOR

®

VIH

@

O.2V

5-94