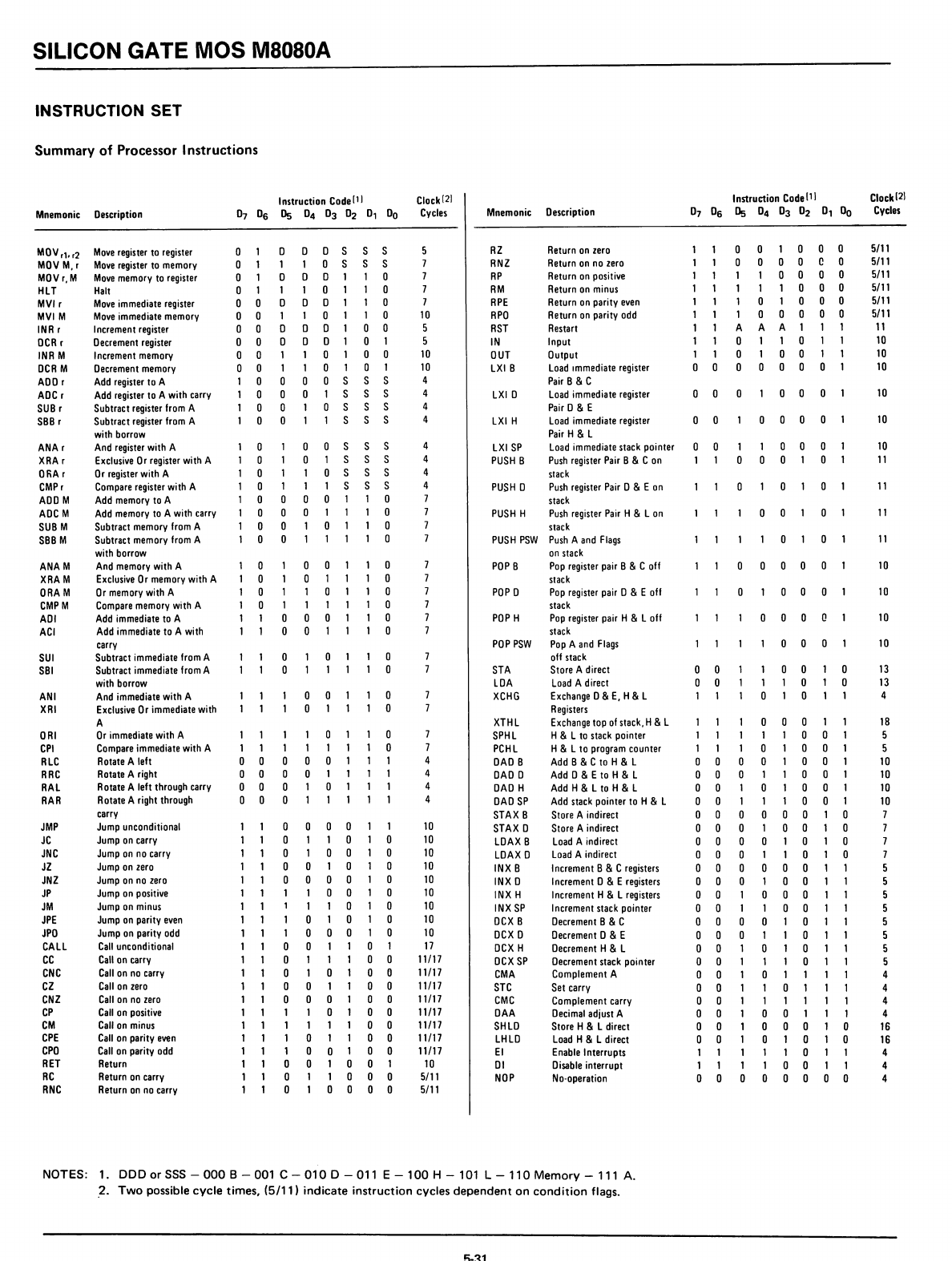

SILICON GATE MOS M8080A

INSTRUCTION SET

Summary

of

Processor

Instructions

Instruction

Code

(1)

Clock

(21

Instruction

Code

[n

Clock

(2)

Mnemonic

Description

07

06

Os

04

03 02

0,

Do

Cycles

Mnemonic

Description

07

06

Os

04

03 02

0

1

00

Cycles

MOV

r1

,r2

Move

register

to

register

0

1 0 0

0

S

S

S

5

RZ

Return

on

zero

1

1

0

0

1

0 0 0

5/11

MOV

M,r

Move

register

to

memory

0

1

1

1 0

S

S

S

7

RNZ

Return

on

no

zero

1

1

0

0 0 0

C

0

5/11

MOVr,M

Move

memory

to

register

0

1 0

0 0

1 1

0

7

RP

Return

on

positive

1

1 1 1

0

0 0 0

5/11

HlT

Halt

0

1

1 1

0

1 1

0

7

RM

Return

on

minus

1 1

1 1

1

0

0 0

5/11

MVIr

Move

immediate

register

0 0

0

0 0

1

1

0

7

RPE

Return

on

parity

even

1 1

1 0

1

0 0

0

5/11

MVIM

Move

immediate

memory

0 0

1

1

0

1

1

0

10

RPO

Return

on

parity

odd

1

1

1 0

0 0

0

0

5/11

INR

r

I

ncrement

register

0

0

0

0

0

1 0 0 5

RST

Restart

1 1 A A

A

1 1 1

11

OCR

r

Decrement

register

0

0

0

0 0

1 0

1

5

IN

Input

1

1

0

1 1

0

1 1

10

INR

M

I

ncrement

memory

0 0

1

1

0

1 0

0

10

OUT

Output 1

1

0

1

0

0

1

1

10

OCR

M

Decrement

memory

0 0

1 1

0

1 0

1

10

LXI

B

Load

Immediate

register

0

0

0

0 0

0 0

1

10

ADO

r

Add

register

to

A

1

0

0 0

0

S

S

S

4

Pair

B& C

ADC

r

Add

register

to

A

with

carry

1

0 0 0

1

S

S S

4

LXI

0

Load

immediate

register

0

10

SUB

r

Subtract

register

from

A

1

0 0

1 0 S S

S

4

Pair

0 & E

SBB

r

Subtract

register

from

A 1

0

0

1 1

S

S S

4

LXI

H

Load

immediate

register

10

with

borrow

Pair

H& L

ANA

r

And

register

with

A

0

1

0 0 S S S

4

LXISP

Load

immediate

stack

pointer

0 0

10

XRA

r

Exclusive

Or

register

with

A

0

1 0 1 S S

S

4

PUSH

B

Push

register

Pair

B& C

on

0

0

11

ORA

r

Or

register

with

A

0

1 1

0 S

S

S

4

stack

CMPr

Compare

register

with

A

0

1 1 1

S

S S

4

PUSH

0

Push

register

Pair

0 & E

on

11

ADD

M

Add

memory

to

A

0 0 0 0

1

1

0

7

stack

AOC

M

Add

memory

to

A

with

carry

0

0

0

1 1 1

0

7

PUSH

H

Push

register

Pair

H& L

on

11

SUB

M

Subtract

memory

from

A

0 0

1

0

1 1

0

7

stack

SBB

M Subtract

memory

from

A

0 0

1

1

1

1

0

7

PUSH

PSW

Push

A

and

Flags

0 0

11

with

borrow

on

stack

ANAM

And

memory

with

A

0

1

0 0

POP

B

Pop

register

pair

B& C

off

0

10

XRA

M

Exclusive

ar

memory

with

A

0 1 0 0

stack

ORA

M

Or

memory

with

A

0

1 1

0

POP

0

Pop

register

pair

0 & E

off

10

CMPM

Compare

memory

with

A

0

1 1

0

stack

ADI

Add

immediate

to

A

1

0 0 0

POP

H

Pop

register

pair

H& L

off

10

ACI

Add

immediate

to

A

with

1

0 0

0

stack

carry

POP

PSW

Pop

A

and

Flags

10

SUI

Subtract

immediate

from

A

off

stack

SBI

Subtract

immediate

from

A

STA

Store A

direct

0

0

0

13

with

borrow

LOA

Load

A

direct

0

0

0

13

ANI

And

immediate

with

A 0

0

XCHG

Exchange

0 &

E,

H& L

1

0

1 4

XRI

Exclusive

Or

immediate

with

0 0

Registers

A

XTHL

Exchange

top

of

stack,

H& L

1

1

1 0

0

0

1

1

18

ORI

Or

immediate

with

A

1 1

1 1

0

7

SPHL

H& L

to

stack

pointer

1

1

1 1

1

0

0

1

5

CPI

Compare

immediate

with

A

1 1 1 1 1

7

PCHL

H& L

to

program

counter

1

1

1

0

1

0 0 1

5

RLC

Rotate

A

left

0

0 0 0

0

4

DAD

B

Add

B& C

to

H& L

0

0

0

0 1

0 0

1

10

RRC

Rotate

A

right

0 0

0 0

1

4

DAD

0

Add

0 & E

to

H& L

0

0 0

1

1

0 0 1

10

RAL

Rotate

A

left

through

carry

0 0

0

1

0 4

DAD

H

Add

H& L

to

H& L

0

0

1

0 1

0 0

1

10

RAR

Rotate

A

right

through

0

0 0

1 1

4

DAD

SP

Add

stack

pointer

to

H& l

0 0

1

1 1

0 0

1

10

carry

STAX

B

Store

A

indirect

0

0

0 0

0

0

1

0

7

JMP

Jump

unconditional

0 0

0 0

1 1

10

STAX

0

Store

A

indirect

0

0

0

1

0 0

1

0 7

JC

Jump

on

carry

0

1

1

0

1

0

10

LOAX

B

Load

A

indirect

0

0

0

0 1

0

1

0 7

JNC

Jump

on

no

carry

0

1

0 0 1

0

10

LOAX

0

Load

A

indirect

0

0

0

1

1

0

1

0

7

JZ

Jump

on

zero

0

0

1

0

1

0

10

INX

B

Increment

B& C

registers

0

0

0 0 0

0

1 1

5

JNZ

Jump

on

no

zero

0

0

0

0

1

0

10

INX

0

Increment

0 & E

registers

0

0 0 1

0

0 1 1

5

JP

Jump

on

positive

1 1

0

0

1

0

10

INX

H

Increment

H& L

registers

0

0 1

0

0

0 1 1

5

JM

Jump

on

minus

1

1 1

0

1

0

10

INX

SP

I

ncrement

stack

pointer

0

0 1 1

0

0

1 1

5

JPE

Jump

on

parity

even

1

0

1

0

1

0

10

OCX

B

Decrement

B& C

0 0

0 0 1

0

1

1

5

JPO

Jump

on

parity

odd

1

0 0 0

1

0

10

OCX

0

Decrement

0 & E

0 0 0

1

1

0

1 1

5

CALL

Call

unconditional

0 0

1

1

0

1

17

OCX

H

Decrement

H& L

0

0

1

0

1

0

1

1

5

CC

Call

on

carry

0

1 1

1 0

0

11/17

OCX

SP

Decrement

stack

pointer

0

0

1

1

1

0

1

1

5

CNC

Call

on

no

carry

0

1

0 1

0

0

11/17

CMA

Complement

A

0

0

1

0 1

1

1

1

4

CZ

Call

on

zero

0 0 1 1

0 0

11/17

STC

Set

carry

0

0

1 1

0

1

1

1

4

CNZ

Call

on

no

zero

0 0 0 1

0

0

11/17

CMC

Complement

carry

0

0

1

1 1

1 1

1

4

CP

Call

on

positive

1

1

0 1

0

0

11/17

OAA

Decimal

adjust

A

0 0 1

0

0 1 1

1

4

CM

Call

on

minus

1 1 1 1

0

0

11/17

SHLD

Store H& l

direct

0

0 1 0

0

0

1

0

16

CPE

Call

on

parity

even

1

0

1

1

0

0

llf17

LHlO

Load

H& L

direct

0 0 1

0 1

0

1

0

16

CPO

Call

on

parity

odd

1

0

0

1

0

0

l1f17

EI

Enable

Interrupts

1 1

1 1

1

0

1

1

4

RET

Return

0 0 1

0 0

1

10

01

Disable

interrupt

1 1

1

1

0

0 1 1

4

RC

Return

on

carry

0

1

1

0 0

0

5/11

NOP

No-operation

0

0

0

0

0

0 0

0

4

RNC

Return

on

no

carry

0

1

0

0

0

0

5/11

NOTES: 1.

DOD

or

SSS

-

000

B - 001 C -

010

0 - 011 E -

100

H -

101

L -

110

Memory

- 111 A.

2.

Two

possible

cycle

times,

(5/11)

indicate

instruction

cycles dependent on

condition

flags.