89

CHAPTER 4 I/O PORTS

● Operation when a reset is performed

When the CPU is reset, the bits of the DDR3 register are initialized to "0", at which time the output

transistors become OFF (input port mode) and the pins become Hi-Z.

However, CPU resets do not initialize the PDR3 register. If a pin is used as an output port after the reset,

reinitialize the PDR3 register to contain new output data in the bit position corresponding to the pin and

then set the corresponding bit of the DDR3 register so that the pin will function as an output port.

● Operation in stop mode

When the pin state setting bit of the standby control register (STBC: SPL) is set to "1" and when the stop

mode is entered, the pin becomes Hi-Z because the output transistor is turned OFF regardless of the value

existing on the DDR3 register in the bit position corresponding to the pin.

Table 4.3-4 summarizes the operating modes of the pins of port 3.

Note:

When the pull-up resistor is selected by using the pull-up setting register, the pin state will be "H" level

instead of Hi-Z in stop mode (SPL = 1). During a reset, however, the pull-up is invalid with the pin

remaining at Hi-Z.

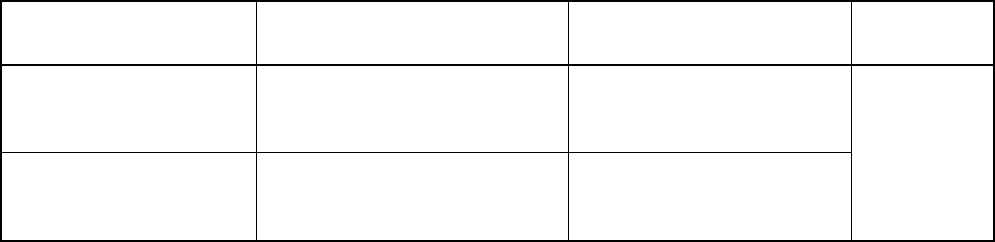

Table 4.3-4 Operating Modes of Pins of Port 3

Pin name

Normal operation, sleep, stop

(SPL = 0)

Stop (SPL = 1) At a reset

P30/UCK/SCK

to

P33/EC, P37/BZ/PPG

General-purpose I/O port may also

serve I/O for peripherals

Hi-Z

Hi-Z

P34/TO/INT10

to

P36/INT12

General-purpose I/O port may also

serve outputs from peripherals and

external interrupt inputs

Hi-Z

(External interrupt input)

SPL : Pin state setting bit of standby control register (STBC: SPL)

Hi-Z: High impedance