58

CHAPTER 3 CPU

3.6.4 Clock Mode

The clock speed is switched by selecting one of four frequency-divided source clocks

(gears).

■ Operations in Each Clock Mode

Each clock mode allows transition to a corresponding standby (sleep/stop) mode. For details of standby

mode, see Section "3.7 Standby Mode (Low-Power Consumption Mode) ".

■

Gears (Clock Speed Switching Function)

Writing one of 00

B

to 11

B

into the clock speed selection bits (SYCC: CS1 and CS0) in the system clock

control register selects one of four clock speeds.

The CPU and peripheral circuits operate using the clock speed selected. However, the gear does not affect

the time-base timer.

Power consumption can be reduced by lowering the clock speed.

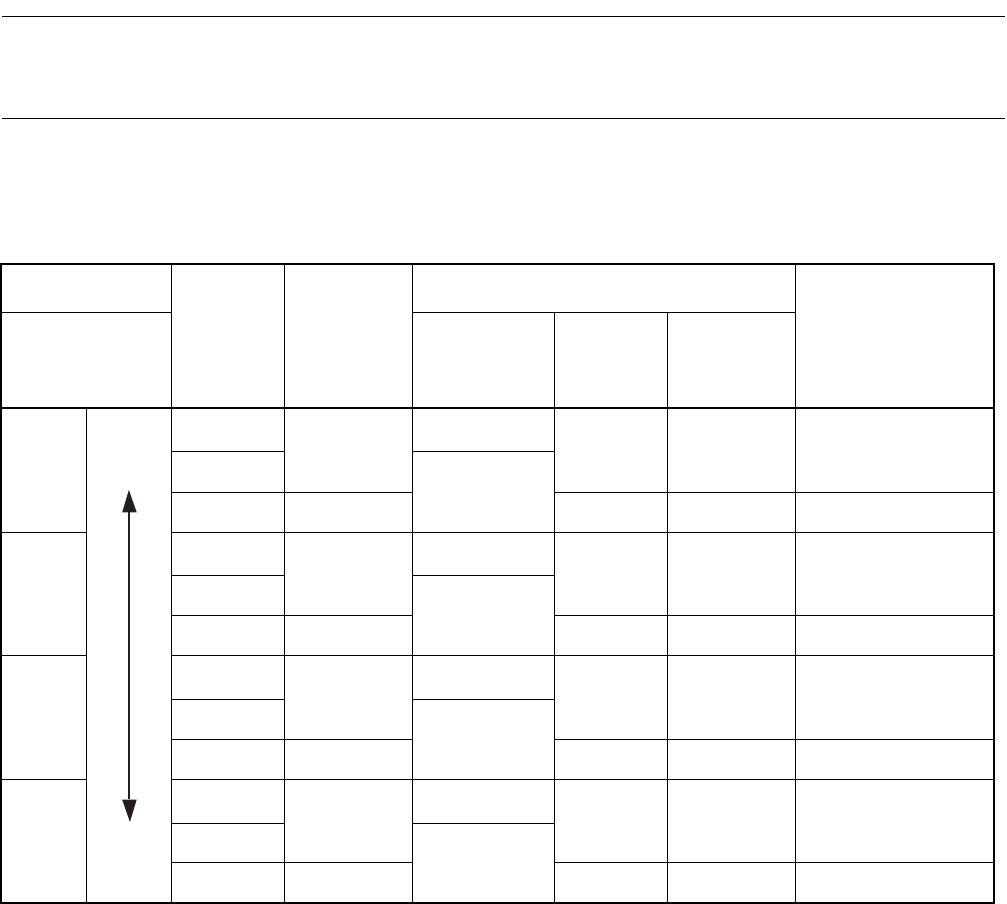

Table 3.6-2 Operations in Each Clock Mode

Clock speed

Standby

mode

Clock

Operating clock in each block

Cause that cancels

standby mode

(excepting reset)

SYCC register

(SYCC: CS1

and CS0)

CPU

time-base

timer

Peripheral

function

(1, 1)

High

speed

Low

speed

RUN

Generated

F

CH

/4

F

CH

/2 F

CH

/4

Interrupt request

Sleep

Stopped

Stop Stopped Stopped Stopped External interrupt

(1, 0)

RUN

Generated

F

CH

/8

F

CH

/2 F

CH

/8

Interrupt request

Sleep

Stopped

Stop Stopped Stopped Stopped External interrupt

(0, 1)

RUN

Generated

F

CH

/16

F

CH

/2 F

CH

/16

Interrupt request

Sleep

Stopped

Stop Stopped Stopped Stopped External interrupt

(0, 0)

RUN

Generated

F

CH

/64

F

CH

/2 F

CH

/64

Interrupt request

Sleep

Stopped

Stop Stopped Stopped Stopped External interrupt