37

CHAPTER 3 CPU

3.4.2 Steps in the Interrupt Operation

When an interrupt request is generated in a peripheral function, the interrupt controller

notifies the CPU of its interrupt level. If the CPU can accept an interrupt, the CPU

temporarily stops the program that is handling and starts the interrupt processing

routine.

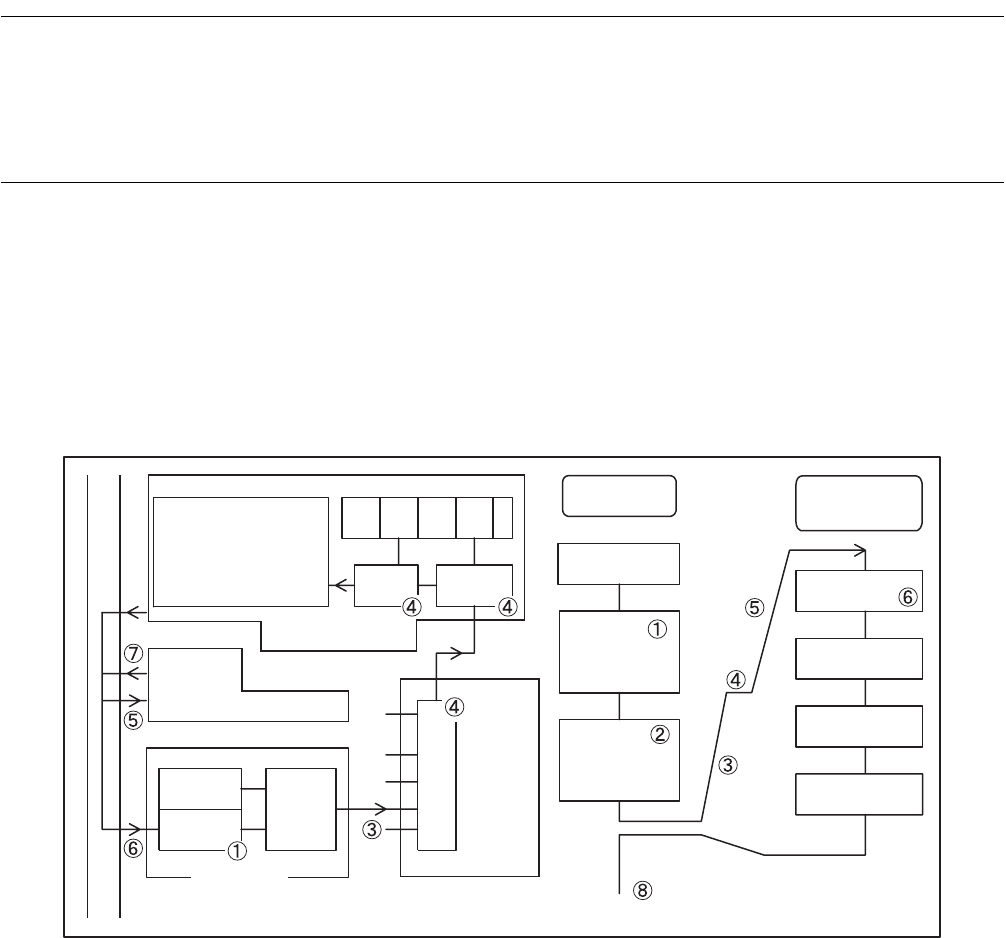

■ Steps in the Interrupt Operation

The steps for processing an interrupt are: occurrence of a source of an interrupt in a peripheral function,

designation of the interrupt request flag bit (request F/F), check on the interrupt request enable bit (enable

F/F), check on the interrupt level (ILR1, 2, 3, or 4, and CCR: IL1 and IL0), check on another request with

the same level, and check on the interrupt enable flag (CCR: I).

Figure 3.4-2 shows the steps in the interrupt operation.

Figure 3.4-2 Steps in the Interrupt Operation

➀ After a reset, all interrupt requests are prohibited.

Initialize the peripheral functions that generate interrupts using a initialization program for peripheral

functions, specify interrupt levels in the interrupt level setting registers (ILR1 to ILR4) concerned, then

start up the peripheral functions.

Interrupt levels 1, 2, and 3 can be specified. Level 1 is the highest level, and level 2 is the second

highest level. Level 3 prohibits interrupts from the peripheral functions to which it is assigned.

➁ Run the main program. (For a multiple-interrupt, run the interrupt processing routine.)

➂ When a peripheral function generates a source of an interrupt, the interrupt request flag bit for

peripheral function (request F/F) is set to "1". If the interrupt request enable bit for a peripheral function

is turned on (enable F/F = 1) at that time, an interrupt request is output to the interrupt controller.

ILIPS

MB89202 CPU

AND

RAM

Internal bus

Operation

Unit

Check

Com-

parator

Enable

F/F

Source

F/F

Peripheral

Level comparator

Interrupt

controller

Main

program

Cancellation

of a reset

Initial setting

for interrupt

Execution

of main

program

Interrupt

processing

routine

Update of IL

PC and

PS saved

Request

cleared

Level

check

Interrupt

processing

PC and PS

restored

Occur-

rence of

interrupt

RETI

PC and PS

restored

.

.

.