307

CHAPTER 13 UART

13.6.2 Reception Operations (Operating Mode 0, 1, or 3)

When data is received at the serial data input pin, the internal reception shift register

converts it from serial to parallel. If the data is correctly transmitted up to the stop

bit(s), data in the internal shift register is transferred to the SIDR register, then "1" is set

to the RDRF bit.

■ Reception Operations (Operating Mode 0, 1, or 3)

If an overrun error or framing error occurs, the received data is not transmitted to the SIDR register, but the

ORFE bit is set to "1".

Either of the RDRF bit and ORFE bit goes on when the final stop bit is detected after data is fully received.

If the reception interrupt is enabled (SSD: RIE = 1), an interrupt request to the CPU (IRQ6) is generated.

When the RDRF bit goes on, the received data has been transmitted to the SIDR register.

In operating mode 2, when the RIE bit is "1", RDRF bit or ORFE bit is "1", and reception interrupt pin is

"1", the mode 2 UART reception interrupt request is output to the CPU.

Note:

In operating mode 1, the parity bit is read as data in the 7th bit. Set up the program so that the 7th bit is

not read.

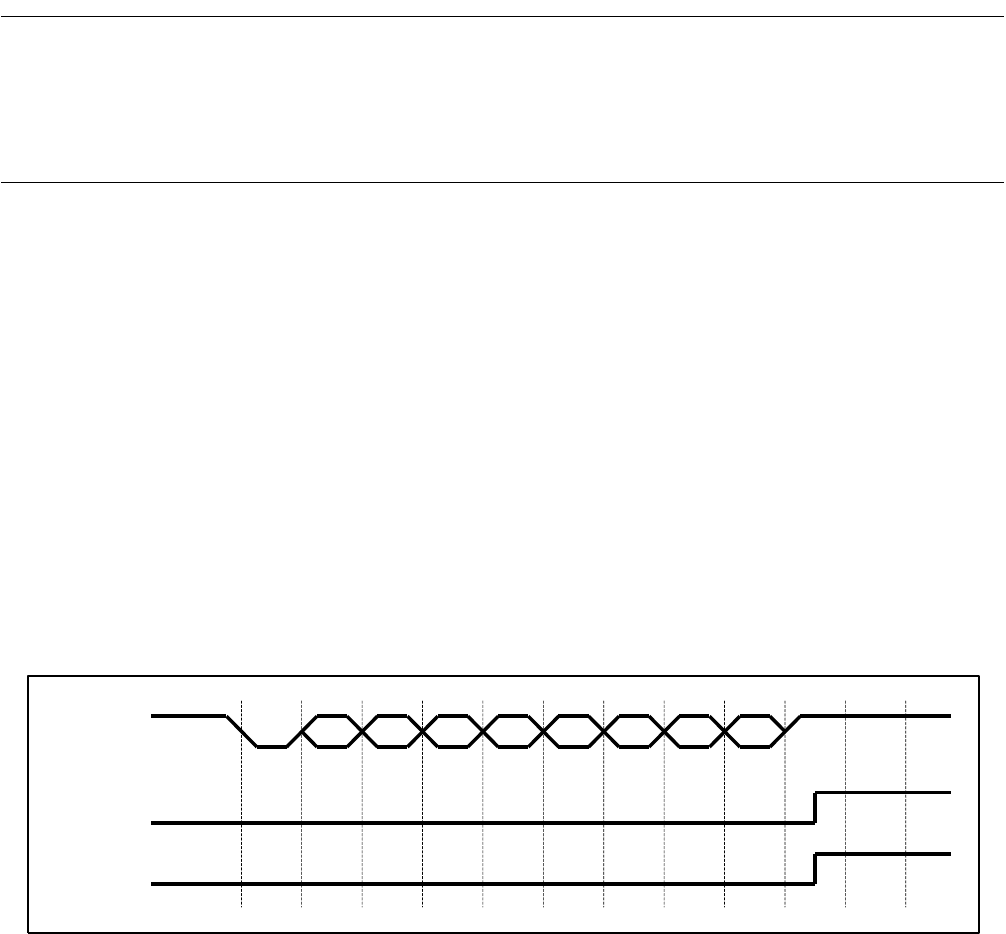

Figure 13.6-4 , Figure 13.6-5 , and Figure 13.6-6 show the reception operations when parity is not used and

the number of stop bits is "1" in operating mode 0, 1, or 3.

Figure 13.6-4 Reception Operations in Operating Mode 0, 1, or 3

RDRF

STOPSTART

01234567

Data

Reception

interrupt