306

CHAPTER 13 UART

13.6.1 Transmission Operations (Operating Mode 0, 1, 2, and 3)

When writing data to be transmitted into the SODR register after reading the SSD

register sends the data written into the SODR register to the transmission shift register,

parallel-serial conversion then starts. The data converted is output at the serial data

output pin from the lowest bit in sequence (with LSB first). When the next data becomes

writable, "1" is set to the TDRE bit, then an interrupt request to the CPU is generated if

the transmission interrupt is allowed (SSD: TIE = 1).

■ Transmission Operations in Operating Mode is 0, 1, 2, or 3

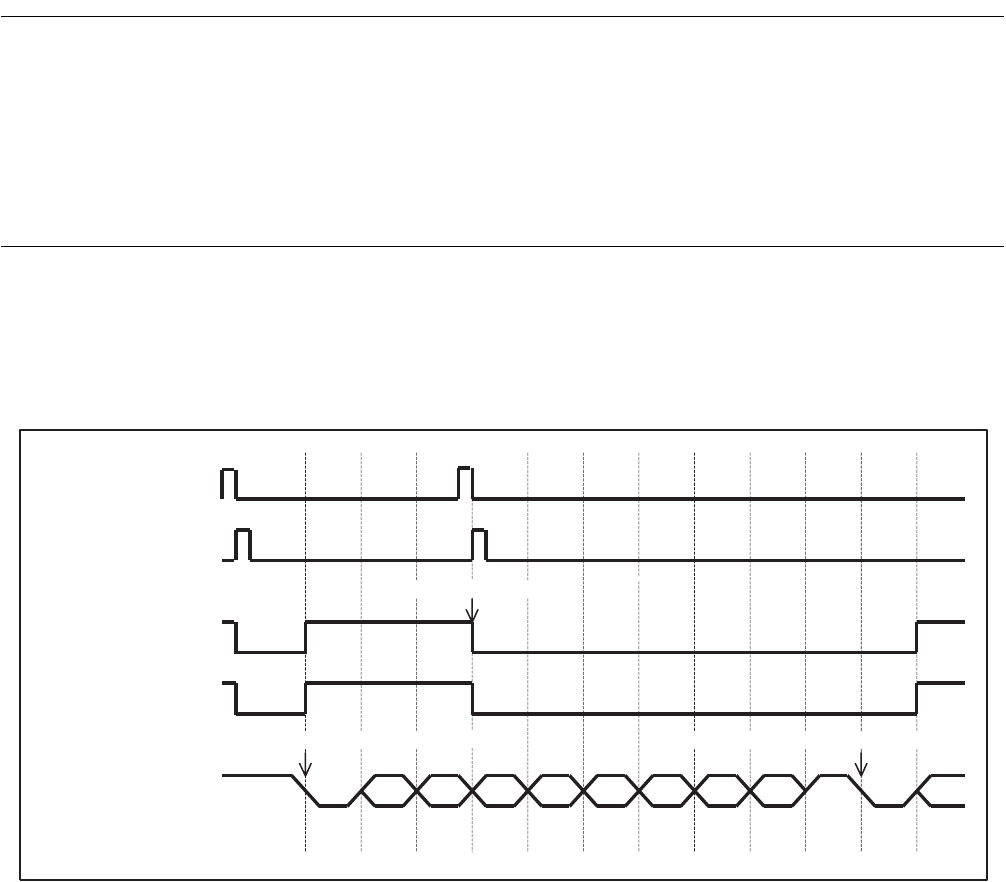

Figure 13.6-3 shows the transmission operations when operating mode is 1, parity is not used, and the

number of stop bits is "1".

Figure 13.6-3 Transmission Operations in Operating Mode 0, 1, 2, or 3

STOPSTART START

01234567

SSD read

SODR write

(interrupt processing

routine)

Transmission interrupt

TDRE

Data transmitted

Transmission buffer full

Sent to the transmission shift register

Sent to the transmission shift register