128

CHAPTER 6 WATCHDOG TIMER

6.1 Overview of Watchdog Timer

The watchdog timer is a 1-bit counter that uses output from the time-base timer, based

on oscillation frequency, as the count clock. The watchdog timer resets the CPU when

not cleared within a specified period after activation.

■ Watchdog Timer Function

The watchdog timer is a counter for preventing programs from hanging up. The timer must be cleared at

specified intervals after being activated. If the timer is not cleared within a specified period of time

because, for example, a program goes into an endless loop, the timer sends to the CPU a watchdog reset

having a period of four instruction cycles.

The watchdog timer uses the output from the time-base timer as the count clock.

The time intervals for the watchdog timer are listed in Table 6.1-1 . When the watchdog timer is not

cleared, a watchdog reset occurs following the time between the minimum time interval and the maximum

time interval. The counter must be cleared before the time of the minimum time interval.

See Section "6.4 Operations of Watchdog Timer Functions " for details on the maximum and minimum

time intervals of the watchdog timer.

Notes:

• The watchdog timer counter is cleared when the time-base counter is cleared (TBTC : TBR = 0)

while output from the time-base timer is selected. Therefore, if the time-base timer counter

supplying the count clock is cleared repeatedly within the time interval of the watchdog timer, the

watchdog timer does not function correctly.

• When switching to sleep or stop mode, the watchdog timer counter is cleared and stops operating

until returning to normal operation (RUN state).

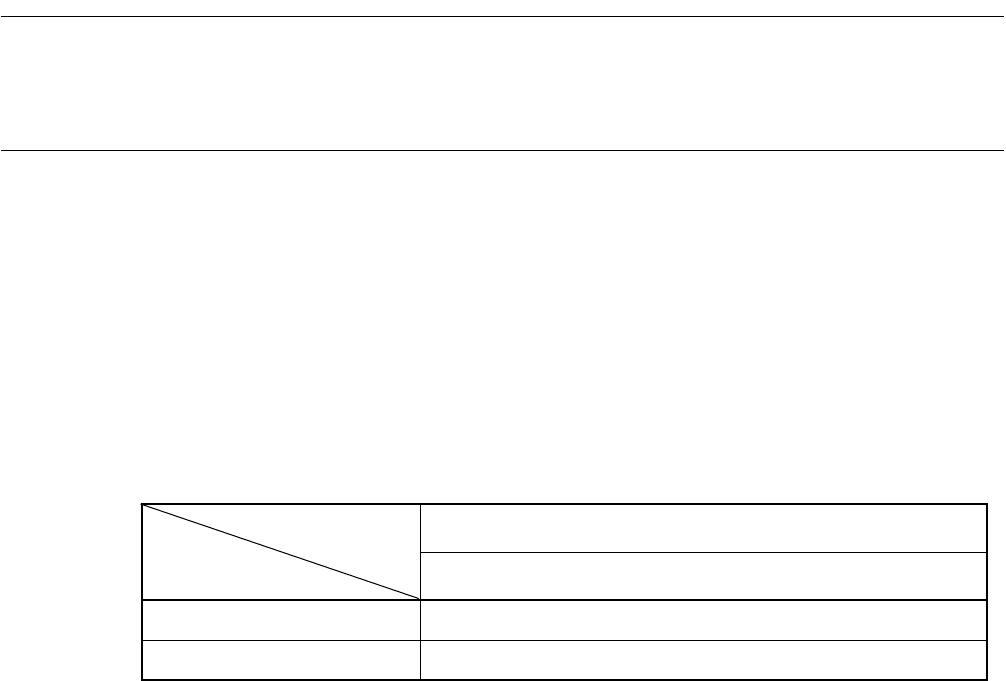

Table 6.1-1 Watchdog Timer Time Intervals

Count clock

Time-base timer output (Oscillation frequency: 12.5 MHz)

Minimum time interval Approximately 335.5 ms *

Maximum time interval Approximately 671.0 ms

*: (number of counts of time-base timer (2

22

)) × (oscillation frequency (F

CH

) divided by 2)