376

APPENDIX A I/O Map

APPENDIX A I/O Map

For the registers of peripheral functions incorporated in the MB89202/F202RA series,

the addresses shown in Table A-1 are assigned.

■ I/O Map

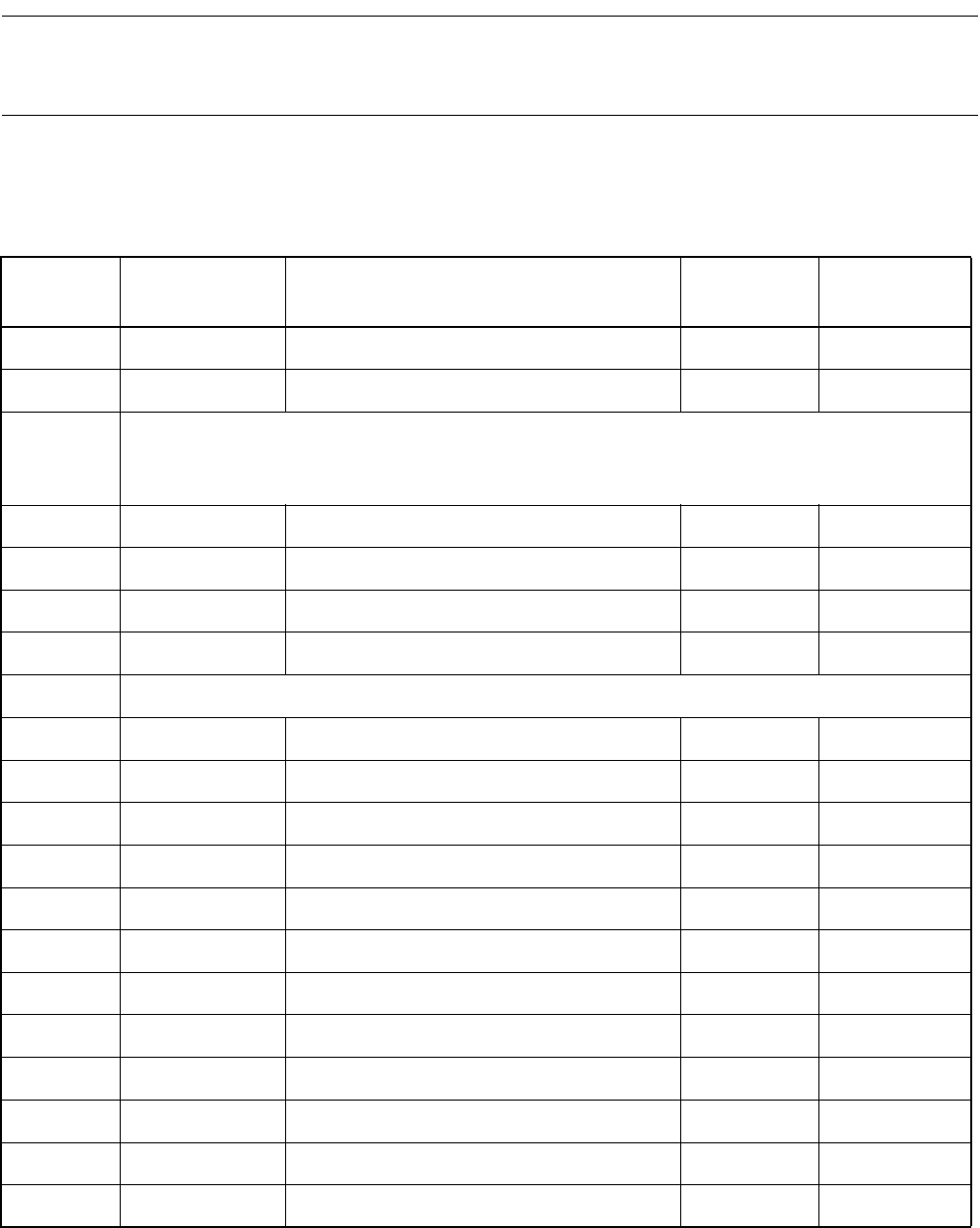

Table A-1 I/O Map (1 / 4)

Address

Register

abbreviation

Register name Read/write Initial value

0000

H

PDR0 Port 0 data register R/W XXXXXXXX

0001

H

DDR0 Port 0 data direction register W 00000000

0002

H

to

0006

H

Vacancy

0007

H

SYCC System clock control register R/W 1--11100

0008

H

STBC Standby control register R/W 00010---

0009

H

WDTC Watchdog control register R/W 0---XXXX

000A

H

TBTC Time-base timer control register R/W 00---000

000B

H

Vacancy

000C

H

PDR3 Port 3 data register R/W XXXXXXXX

000D

H

DDR3 Port 3 data direction register W 00000000

000E

H

RSFR Reset flag register R XXXX----

000F

H

PDR4 Port 4 data register R/W ----XXXX

0010

H

DDR4 Port 4 data direction register R/W ----0000

0011

H

OUT4 Port 4 output format register R/W ----0000

0012

H

PDR5 Port 5 data register R/W -------X

0013

H

DDR5 Port 5 data direction register R/W -------0

0014

H

RCR21 12-bit PPG control register 1 R/W 00000000

0015

H

RCR22 12-bit PPG control register 2 R/W --000000

0016

H

RCR23 12-bit PPG control register 3 R/W 0-000000

0017

H

RCR24 12-bit PPG control register 4 R/W --000000