7

CHAPTER 1 OVERVIEW

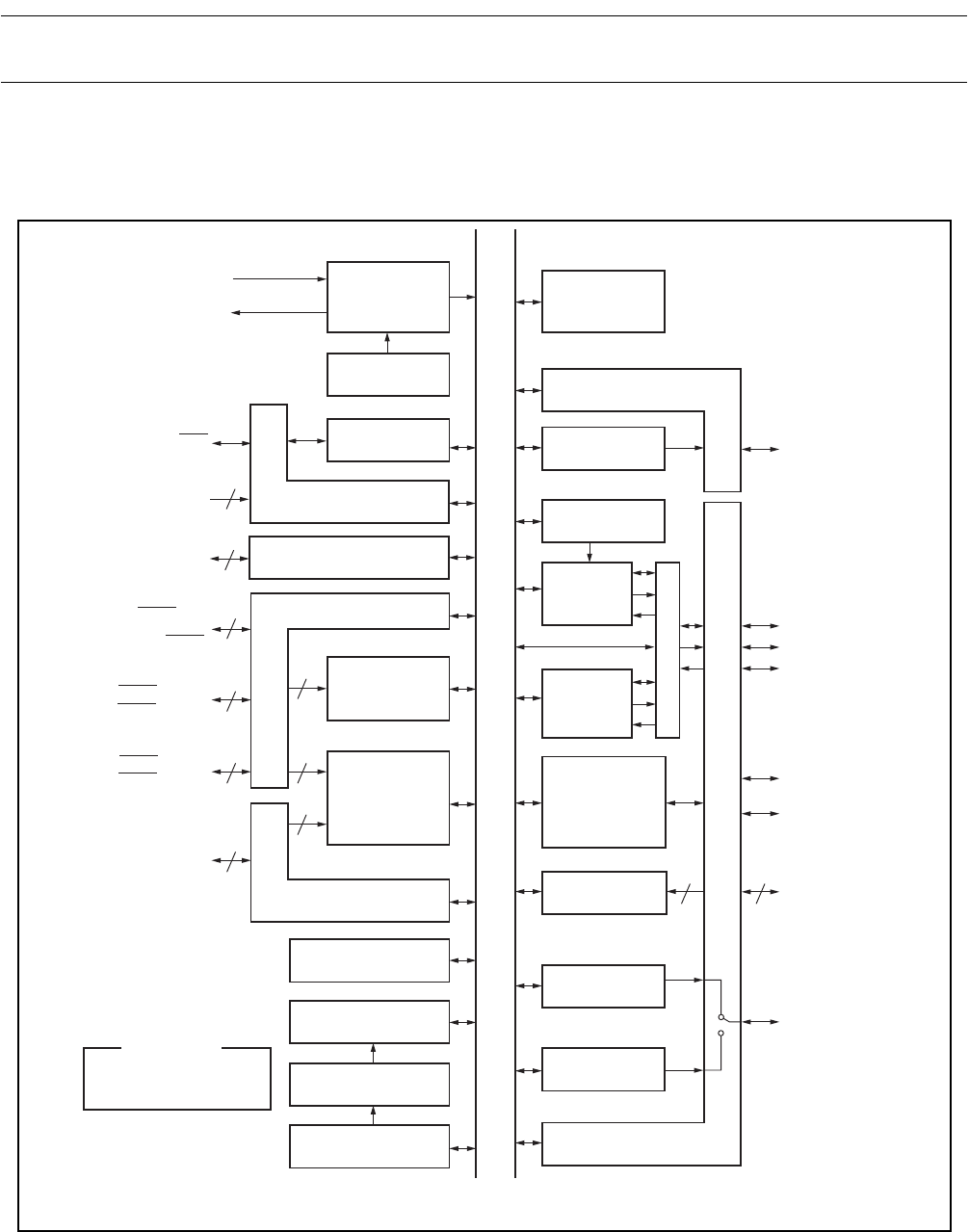

1.4 Block Diagram of MB89202/F202RA Series

Figure 1.4-1 shows the block diagram of the MB89202/F202RA series.

■ Block Diagram of MB89202/F202RA Series

Figure 1.4-1 Block Diagram of MB89202/F202RA Series

X0

X1

RST

P04 / INT24

to

P07 / INT27

P00 / INT20 / AN4,

P01 / INT21 / AN5

*

1

P40 / AN0

to

*

1

P43 / AN3

F

2

MC - 8 L CPU

Wild register

16K or 8K bytes ROM

512 or 256 bytes RAM

CMOS I/O port

(N-ch OD)

10-bit A/D

converter

External

interrupt2

(wake-up)

CMOS I/O port

Reset circuit

Clock controller

Main clock

oscillator

Port 4 Port 0

V

CC

, V

SS

, C

12-bit PPG

Buzzer output

CMOS I/O port

External interrupt1

8/16-bit

capture timer/

counter

8-bit

serial I/O

8-bit PWM

CMOS I/O port

Time-base timer

UART

Internal bus

Port 5Port 3

Serial function switching

UART prescaler

P37 / BZ / PPG

P35 / INT11

P36 / INT12

P34 / TO / INT10

P33 / EC

P32 / UI / SI

P31 / UO / SO

P30 / UCK / SCK

P50 / PWM

4

3

2

P02 / INT22 / AN6,

P03 / INT23 / AN7

2

4

4

8

4

Other pins

CMOS I/O port

Port 6

2

P60, P61

CMOS I/O port

Port 7

3

*

1

P70

to

*

1

P72

*

1

: Large-current drive type

*

2

: Check section "3.1 Memory Space"

*

2

*

2