253

CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT 2 (LEVEL)

11.5 Interrupt of External Interrupt Circuit 2

An "L" level input signal input to one of the external interrupt pins triggers external

interrupt circuit 2 to generate an interrupt.

■ Interrupt during the Operation of External Interrupt Circuit 2

When an "L" level signal is input to one of the external interrupt pins for which interrupt inputs are

enabled, the external interrupt request flag bit (EIF2:IF20) is set to "1" and external interrupt circuit 2

generates and issues an interrupt request (IRQA) to the CPU. Write "0" for the IF20 bit within the interrupt

processing routine, thus clearing the interrupt request.

When the external interrupt request flag bit (IF20) is set to "1", external interrupt circuit 2 generates the

interrupt request, even if external interrupt inputs to the pin are set to disabled by the bit corresponding to

the pin among the interrupt enable bits (IE20 to IE27) of the external interrupt 2 control register (EIE2),

until the IF20 bit is cleared. Therefore, the IF20 bit must always be cleared.

If the "L" level input to the external interrupt pin continues as it is, even if the IF20 bit is cleared with

external interrupt inputs to the pin remaining enabled, the IF20 bit is immediately set to "1" again. Disable

external interrupt inputs to the pin or remove the cause of the external interrupt as required.

Notes:

• When enabling interrupts to the CPU following a release from the reset state, clear the IF20 bit in

advance.

• "L" level inputs to external interrupt pins (INT20

to INT27) trigger external interrupt circuit 2 to

generate the same interrupt request (IRQA). Thus, when an external interrupt input is detected, it is

necessary to identify the pin at which the input occurs by reading the port 0 data register (PDR0)

before the input changes to "H" level.

Only external interrupt circuits 1 and 2 can execute a release from the stop mode by an interrupt.

■

Register Associated with Interrupt Generation by External Interrupt Circuit 2 and

Vector Table

For interrupt operation, see Section "3.4.2 Steps in the Interrupt Operation ".

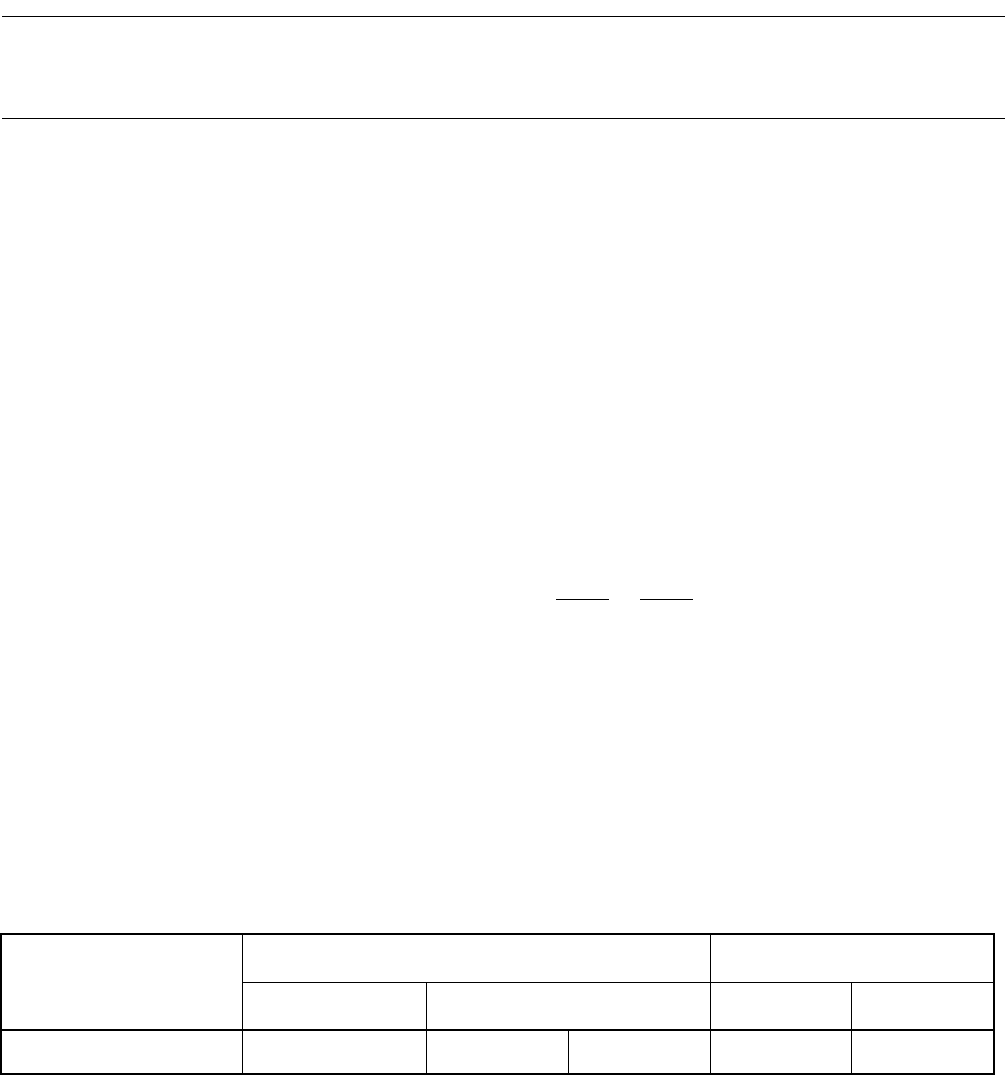

Table 11.5-1 Register Associated with Interrupt Generation by External Interrupt Circuit 2 and Vector

Table

Interrupt designation

Interrupt level setting register Vector table address

Register Bit for setting level Upper Lower

IRQA

ILR3 (007D

H

)

LA1 (bit5) LA0 (bit4)

FFE6

H

FFE7

H