144

CHAPTER 7 8-BIT PWM TIMER

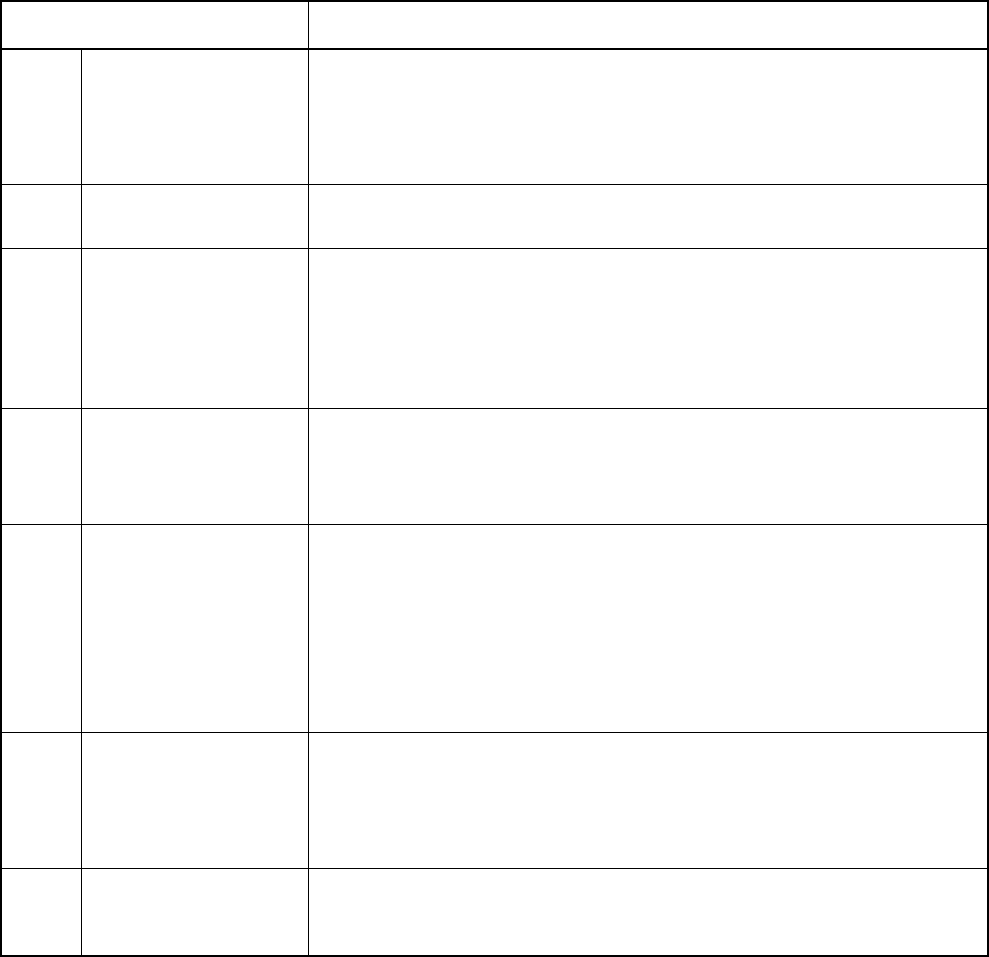

Table 7.4-1 Explanation of the Functions of Each Bit in the PWM Control Register (CNTR)

Bit name Function

bit7

P/TX:

Bit to select the

operation mode

This bit is used to select the interval timer operation (P/TX = 0) or PWM timer

operation (P/TX = 1).

Note:

Before writing into this bit, stop the counter operation (TPE = 0), disable an

interrupt (TIE = 0), and clear the interrupt request flag bit (TIR = 0).

bit6 Unused bit

The value during a read is undetermined.

A write does not affect operations.

bit5,

bit4

P1, P0:

Bits to select the clock

This bit is used to select the count clock of the interval timer functions or PWM

timer functions.

One of three types of internal count clock or the output of the 8/16-bit capture

timer or counter can be selected.

Note:

When the counter is operating (TPE = 1), do not switch P1 and P0.

bit3

TPE:

Bit to enable the counter

operation

This bit is used to start and stop the interval timer functions or PWM timer

functions.

To start the count operation, write "1" to this bit. When "0" is written to this bit,

the counter is cleared (setting 00

H

) and then stopped.

bit2

TIR:

Interrupt request flag bit

While the internal timer functions are enabled:

When the counter value matches the PWM compare register (COMR) value, "1" is

set to this bit.

When this bit and the bit to enable an interrupt request (TIE) are "1", an interrupt

request to the CPU is output.

While the PWM timer functions are enabled, an interrupt request does not occur.

When this bit is written, it is cleared (setting "0"). Writing "1" does not affect this

bit in any way.

bit1

OE:

Bit to control the output

pin

When this bit is "0", the P50/PWM pin is used as a general-purpose port (P50).

When the bit is "1", it is used as a dedicated pin (PWM).

When the interval timer functions are enabled, the square wave is output to the

PWM pin. When the PWM timer functions are enabled, the PWM wave is output

to the PWM pin.

bit0

TIE:

Bit to enable an interrupt

request

This bit is used to enable and disable the output of an interrupt request to the CPU.

When this bit and the interrupt request flag bit (TIR) are both "1", an interrupt

request is output.