56

CHAPTER 3 CPU

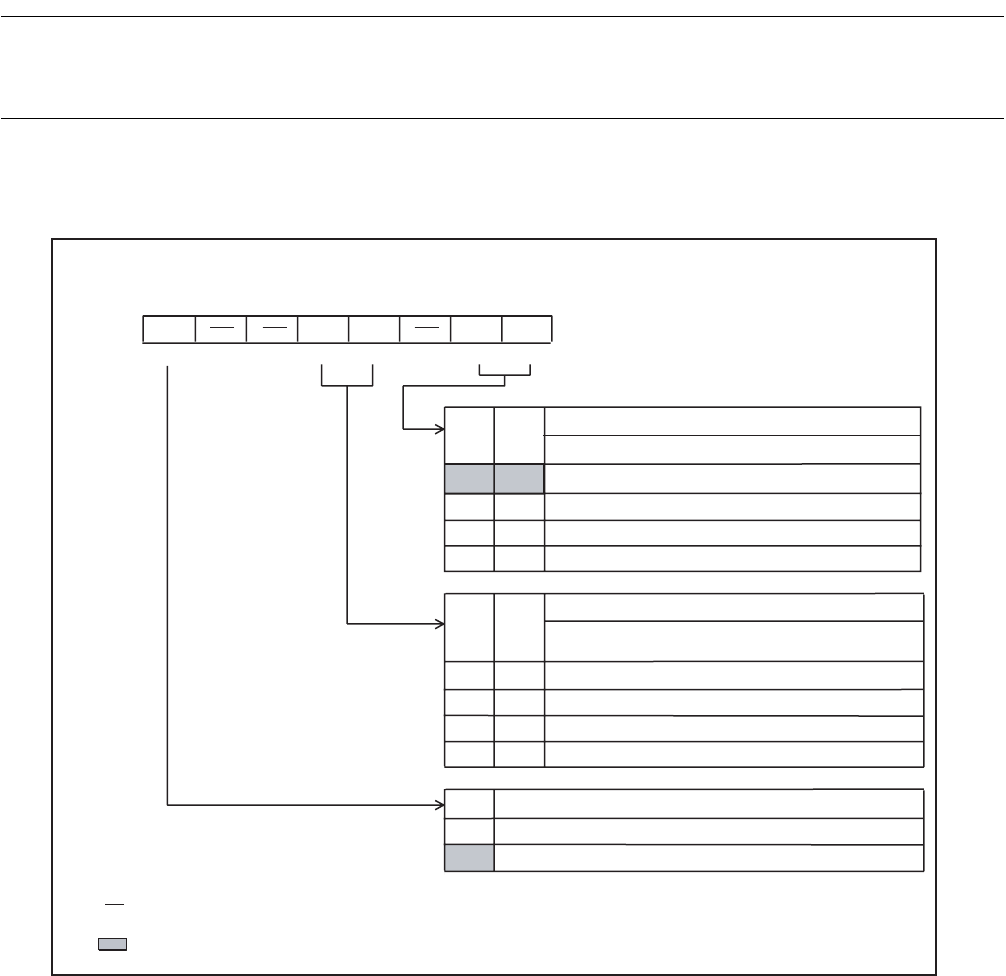

3.6.3 System Clock Control Register (SYCC)

The system clock control register (SYCC) manages clock settings such as selection of

the clock speed and oscillation stabilization wait time.

■ Configuration of the System Clock Control Register (SYCC)

Figure 3.6-5 Configuration of System Clock Control Register (SYCC)

CS1CS0

0

0

64/F

CH

(5.12 µs)

0 1 16/F

CH

(1.28 µs)

108/F

CH

(0.64 µs)

1

1

4/F

CH

(0.32 µs)

WT1 WT0

00

01

10

11

bit7 bit6 bit5 bit4 bit3bit2 bit1 bit0

0007

H

WT1SCM

WT0 CS1

CS0 1--MM-00

B

R/WR R/W R/W R/W

R : Read only

R/W : Readable/Writable

: Unused

M : Mask option

: Initial value

Address

Initial value

Clock speed selection bits

Instruction cycle (when F

CH

is 12.5 MHz)

Oscillation stabilization wait time selection bits

Oscillation stabilization wait time according to

output of the time-base timer (when F

CH is 12.5 MHz)

Setting prohibited

Approx. 2

14

/F

CH

(approx. 1.31 ms)

Approx. 2

17

/F

CH

(approx. 10.5 ms)

Approx. 2

18

/F

CH

(approx. 21.0 ms)

SCM

0

1

System clock monitor bit

Clock stopping or waiting for stabilization of oscillation

Active mode